|

|

楼主 |

发表于 2013-1-25 21:43:18

|

显示全部楼层

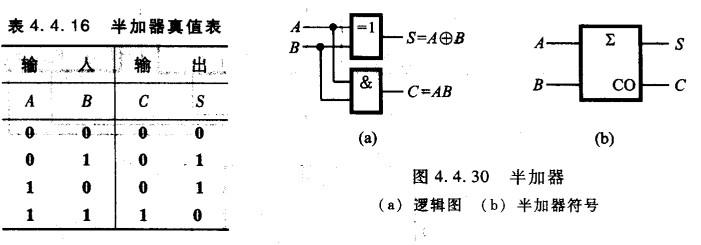

1位半加器

【例7.9】调用门元件实现的1位半加器

module half_add1(a,b,sum,cout);

input a,b;

output sum,cout;

and (cout,a,b);

xor (sum,a,b);

endmodule

【例7.10】数据流方式描述的1位半加器

module half_add2(a,b,sum,cout);

input a,b;

output sum,cout;

assign sum=a^b;

assign cout=a&b;

endmodule

【例7.11】采用行为描述的1位半加器

module half_add3(a,b,sum,cout);

input a,b;

output sum,cout;

reg sum,cout;

always @(a or b)

begin

case ({a,b}) //真值表描述

2'b00: begin sum=0; cout=0; end

2'b01: begin sum=1; cout=0; end

2'b10: begin sum=1; cout=0; end

2'b11: begin sum=0; cout=1; end

endcase

end

endmodule

【例7.12】采用行为描述的1位半加器

module half_add4(a,b,sum,cout);

input a,b;

output sum,cout;

reg sum,cout;

always @(a or b)

begin

sum= a^b;

cout=a&b;

end

endmodule

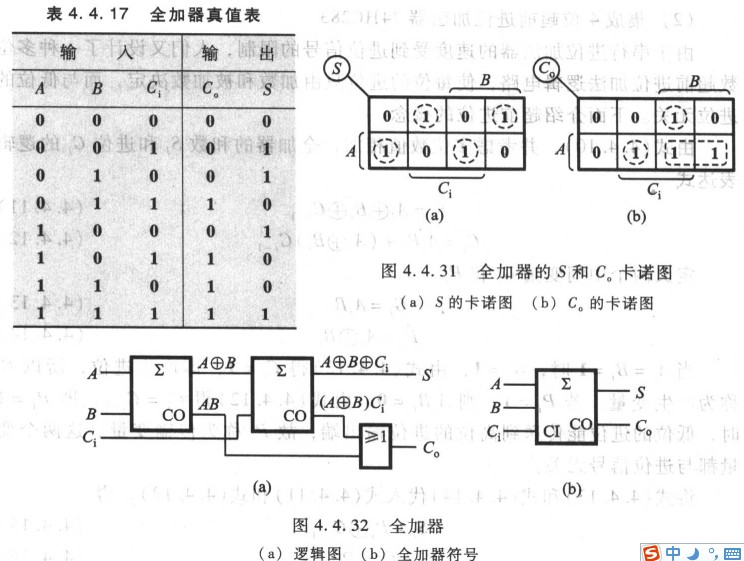

【例7.17】混合描述的1位全加器

module full_add5(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

reg cout,m1,m2,m3; //在always块中被赋值的变量应定义为reg型

wire s1;

xor x1(s1,a,b); //调用门元件

always @(a or b or cin) //always块语句

begin

m1 = a & b;

m2 = b & cin;

m3 = a & cin;

cout = (m1| m2) | m3;

end

assign sum = s1 ^ cin; //assign持续赋值语句

endmodule |

|

发表于 2013-1-25 16:23:53

发表于 2013-1-25 16:23:53

楼主

楼主