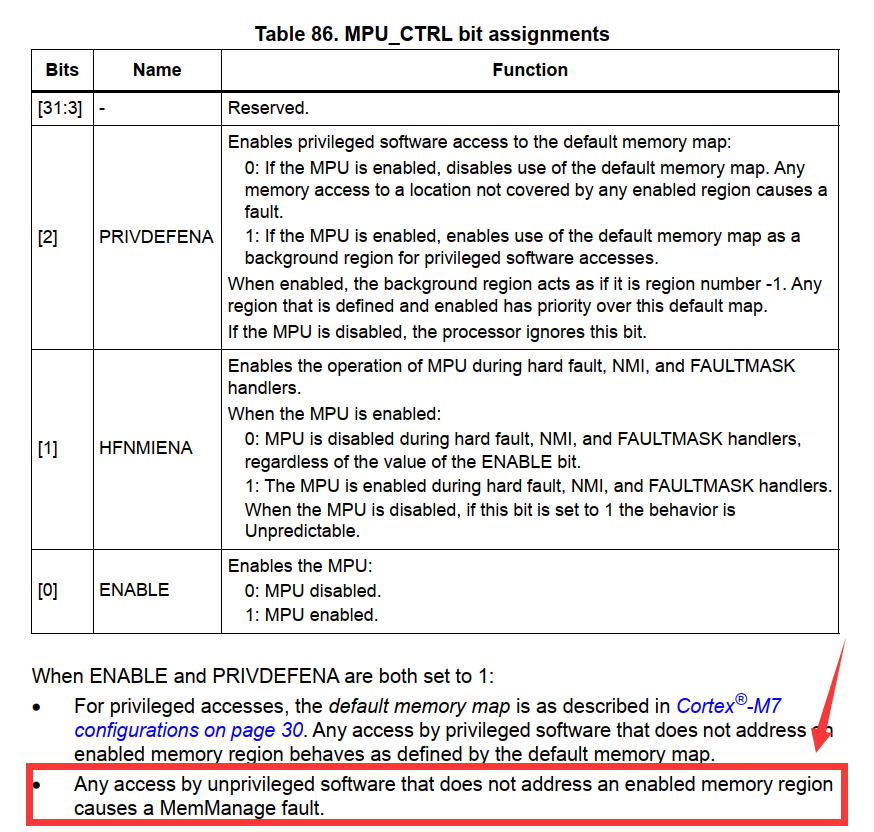

昨晚倒腾了下,发现仅需前1GB空间任意配置个MPU策略,就可以正常使用,真是诡异至极,比如我下面是配置为最高性能,竟然也正常。

看来这个里面还有猫腻,后面有时间再深究下。

[C] 纯文本查看 复制代码 MPU_InitStruct.Enable = MPU_REGION_ENABLE;

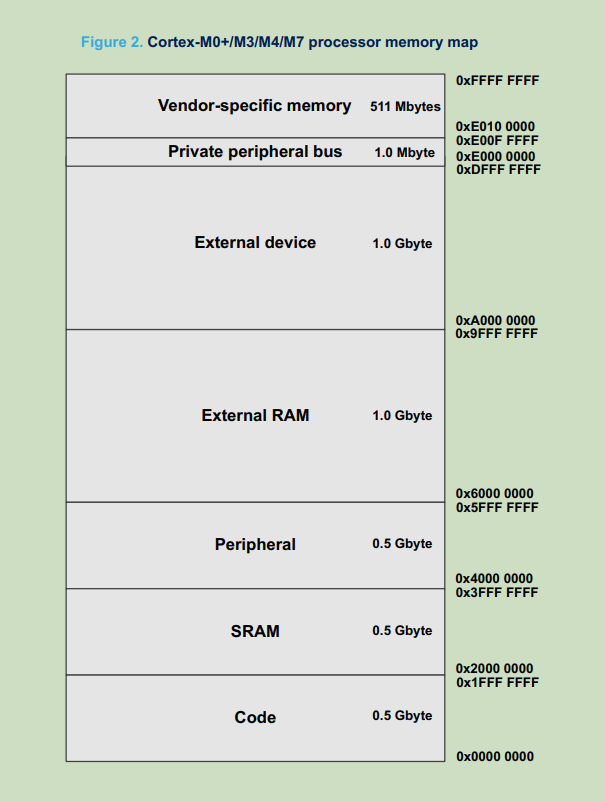

MPU_InitStruct.BaseAddress = 0x00000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_1GB;

MPU_InitStruct.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_InitStruct.IsBufferable = MPU_ACCESS_BUFFERABLE;

MPU_InitStruct.IsCacheable = MPU_ACCESS_CACHEABLE;

MPU_InitStruct.IsShareable = MPU_ACCESS_NOT_SHAREABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER0;

MPU_InitStruct.TypeExtField = MPU_TEX_LEVEL1;

MPU_InitStruct.SubRegionDisable = 0x00;

MPU_InitStruct.DisableExec = MPU_INSTRUCTION_ACCESS_ENABLE;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

|

发表于 2022-4-22 11:03:21

发表于 2022-4-22 11:03:21

发表于 2022-4-22 11:44:18

发表于 2022-4-22 11:44:18

楼主

楼主