[Lua] 纯文本查看 复制代码

print("------------------------------------------------------------------------")

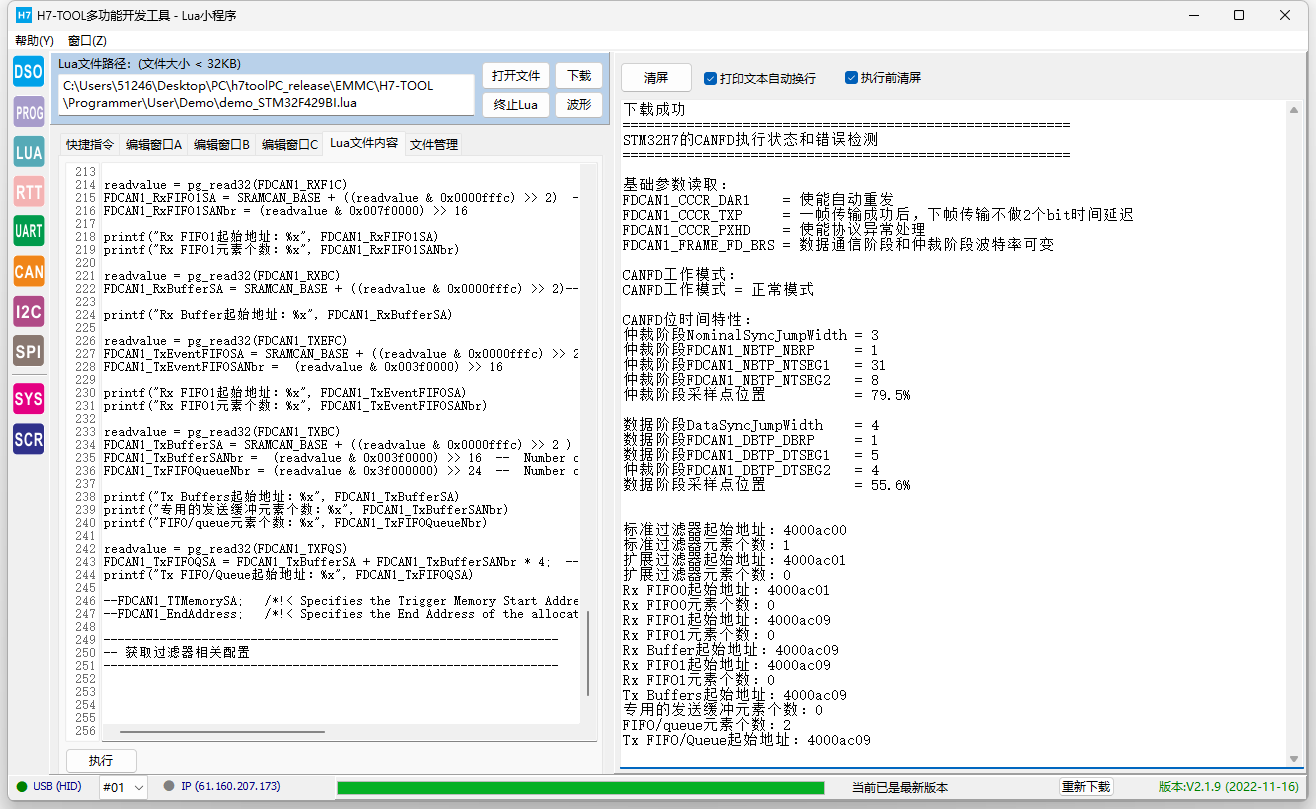

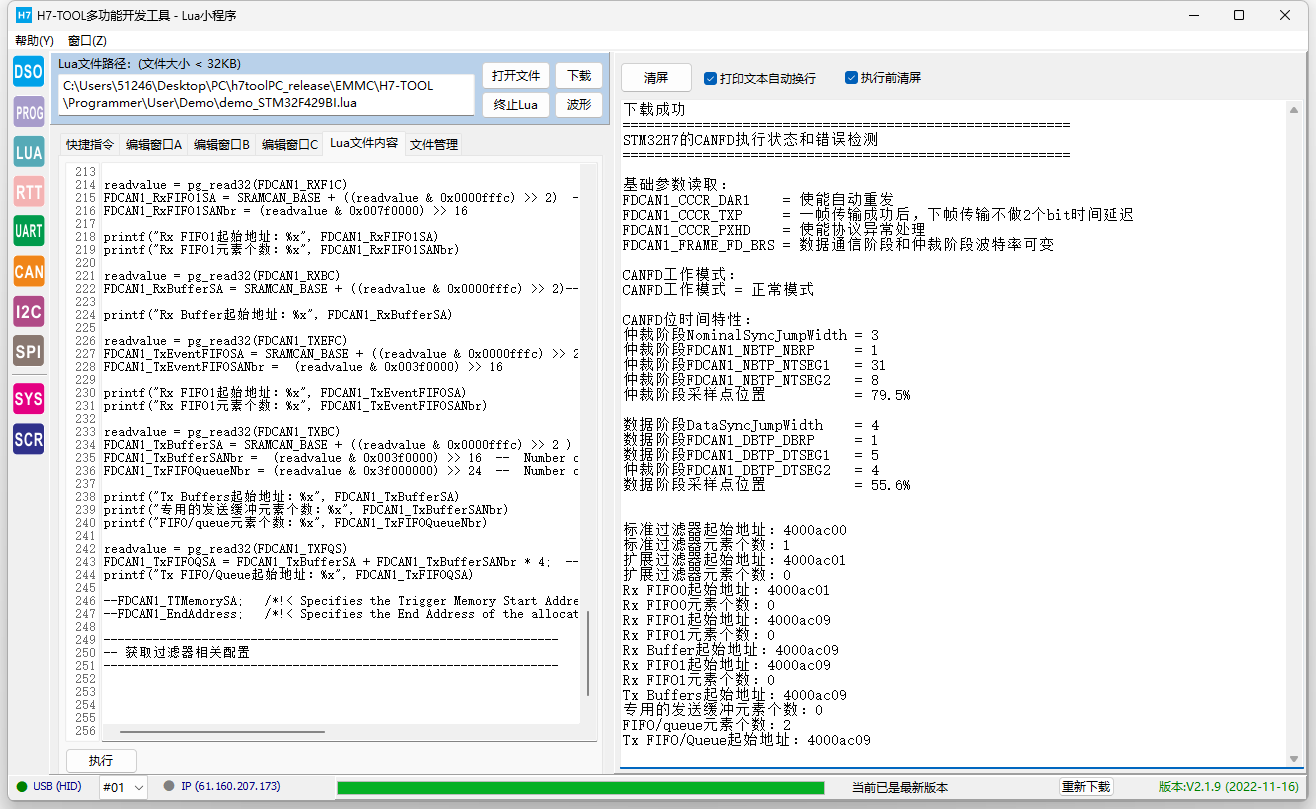

print("STM32H7的CANFD执行状态和错误检测")

print("------------------------------------------------------------------------")

------------------------------------------------------------------------------------

------------------------------------------------------------------------------------

local FDCAN1_MessageRAMOffset = 0

local FDCAN2_MessageRAMOffset = 1280

------------------------------------------------------------------------------------

------------------------------------------------------------------------------------

local PERIPH_BASE = 0x40000000 --/*!< Base address of : AHB/APB Peripherals

local D2_APB1PERIPH_BASE = PERIPH_BASE

local FDCAN1_BASE = D2_APB1PERIPH_BASE + 0xA000

local FDCAN2_BASE = D2_APB1PERIPH_BASE + 0xA400

local FDCAN_CCU_BASE = D2_APB1PERIPH_BASE + 0xA800

local SRAMCAN_BASE = D2_APB1PERIPH_BASE + 0xAC00

------------------------------------------------------------------------------------

-- FDCAN Register

------------------------------------------------------------------------------------

local FDCAN1_CREL = FDCAN1_BASE + 0x000

local FDCAN1_ENDN = FDCAN1_BASE + 0x004

local FDCAN1_RESERVED1 = FDCAN1_BASE + 0x008

local FDCAN1_CREL = FDCAN1_BASE + 0x000 --/*!< FDCAN Core Release register, Address offset: 0x000 */

local FDCAN1_ENDN = FDCAN1_BASE + 0x004 --/*!< FDCAN Endian register, Address offset: 0x004 */

local FDCAN1_RESERVED1 = FDCAN1_BASE + 0x008 --/*!< Reserved, 0x008 */

local FDCAN1_DBTP = FDCAN1_BASE + 0x00C --/*!< FDCAN Data Bit Timing & Prescaler register, Address offset: 0x00C */

local FDCAN1_TEST = FDCAN1_BASE + 0x010 --/*!< FDCAN Test register, Address offset: 0x010 */

local FDCAN1_RWD = FDCAN1_BASE + 0x014 --/*!< FDCAN RAM Watchdog register, Address offset: 0x014 */

local FDCAN1_CCCR = FDCAN1_BASE + 0x018 --/*!< FDCAN CC Control register, Address offset: 0x018 */

local FDCAN1_NBTP = FDCAN1_BASE + 0x01C --/*!< FDCAN Nominal Bit Timing & Prescaler register, Address offset: 0x01C */

local FDCAN1_TSCC = FDCAN1_BASE + 0x020 --/*!< FDCAN Timestamp Counter Configuration register, Address offset: 0x020 */

local FDCAN1_TSCV = FDCAN1_BASE + 0x024 --/*!< FDCAN Timestamp Counter Value register, Address offset: 0x024 */

local FDCAN1_TOCC = FDCAN1_BASE + 0x028 --/*!< FDCAN Timeout Counter Configuration register, Address offset: 0x028 */

local FDCAN1_TOCV = FDCAN1_BASE + 0x02C --/*!< FDCAN Timeout Counter Value register, Address offset: 0x02C */

local FDCAN1_RESERVED2 = FDCAN1_BASE + 0x030 --/*!< Reserved, 0x030 - 0x03C */

local FDCAN1_ECR = FDCAN1_BASE + 0x040 --/*!< FDCAN Error Counter register, Address offset: 0x040 */

local FDCAN1_PSR = FDCAN1_BASE + 0x044 --/*!< FDCAN Protocol Status register, Address offset: 0x044 */

local FDCAN1_TDCR = FDCAN1_BASE + 0x048 --/*!< FDCAN Transmitter Delay Compensation register, Address offset: 0x048 */

local FDCAN1_RESERVED3 = FDCAN1_BASE + 0x04C --/*!< Reserved, 0x04C */

local FDCAN1_IR = FDCAN1_BASE + 0x050 --/*!< FDCAN Interrupt register, Address offset: 0x050 */

local FDCAN1_IE = FDCAN1_BASE + 0x054 --/*!< FDCAN Interrupt Enable register, Address offset: 0x054 */

local FDCAN1_ILS = FDCAN1_BASE + 0x058 --/*!< FDCAN Interrupt Line Select register, Address offset: 0x058 */

local FDCAN1_ILE = FDCAN1_BASE + 0x05C --/*!< FDCAN Interrupt Line Enable register, Address offset: 0x05C */

local FDCAN1_RESERVED48 = FDCAN1_BASE + 0x060 --/*!< Reserved, 0x060 - 0x07C */

local FDCAN1_GFC = FDCAN1_BASE + 0x080 --/*!< FDCAN Global Filter Configuration register, Address offset: 0x080 */

local FDCAN1_SIDFC = FDCAN1_BASE + 0x084 --/*!< FDCAN Standard ID Filter Configuration register, Address offset: 0x084 */

local FDCAN1_XIDFC = FDCAN1_BASE + 0x088 --/*!< FDCAN Extended ID Filter Configuration register, Address offset: 0x088 */

local FDCAN1_RESERVED5 = FDCAN1_BASE + 0x08C --/*!< Reserved, 0x08C */

local FDCAN1_XIDAM = FDCAN1_BASE + 0x090 --/*!< FDCAN Extended ID AND Mask register, Address offset: 0x090 */

local FDCAN1_HPMS = FDCAN1_BASE + 0x094 --/*!< FDCAN High Priority Message Status register, Address offset: 0x094 */

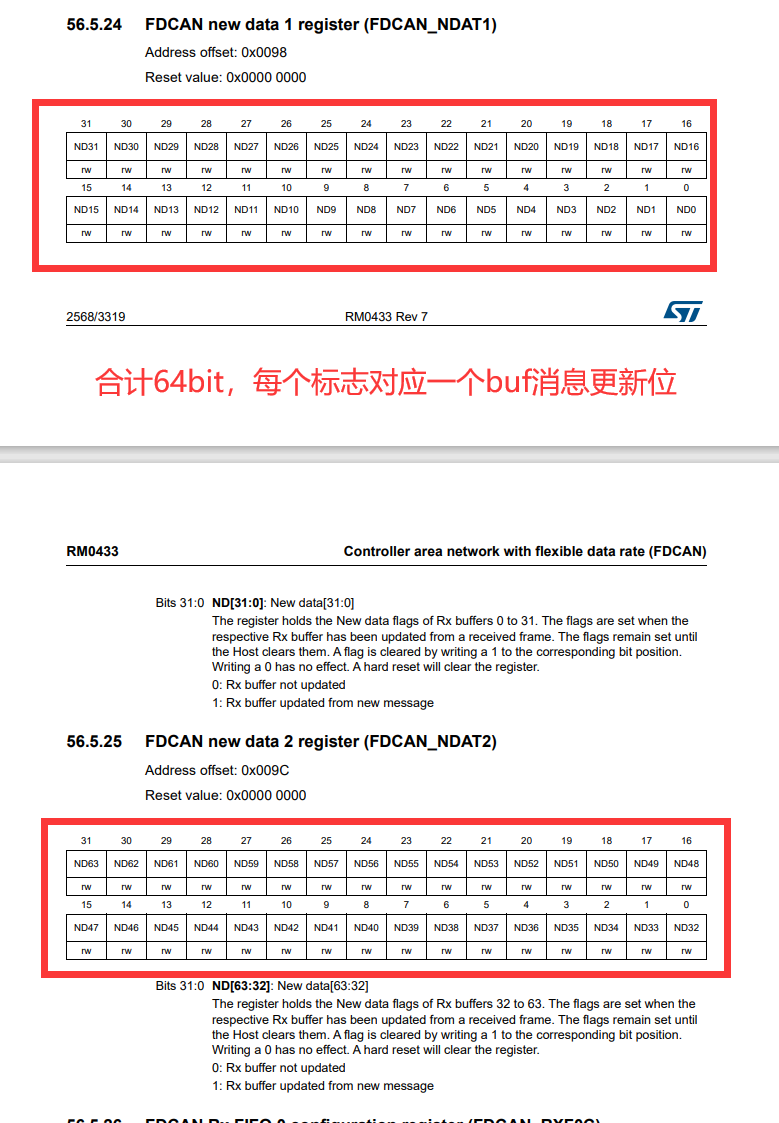

local FDCAN1_NDAT1 = FDCAN1_BASE + 0x098 --/*!< FDCAN New Data 1 register, Address offset: 0x098 */

local FDCAN1_NDAT2 = FDCAN1_BASE + 0x09C --/*!< FDCAN New Data 2 register, Address offset: 0x09C */

local FDCAN1_RXF0C = FDCAN1_BASE + 0x0A0 --/*!< FDCAN Rx FIFO 0 Configuration register, Address offset: 0x0A0 */

local FDCAN1_RXF0S = FDCAN1_BASE + 0x0A4 --/*!< FDCAN Rx FIFO 0 Status register, Address offset: 0x0A4 */

local FDCAN1_RXF0A = FDCAN1_BASE + 0x0A8 --/*!< FDCAN Rx FIFO 0 Acknowledge register, Address offset: 0x0A8 */

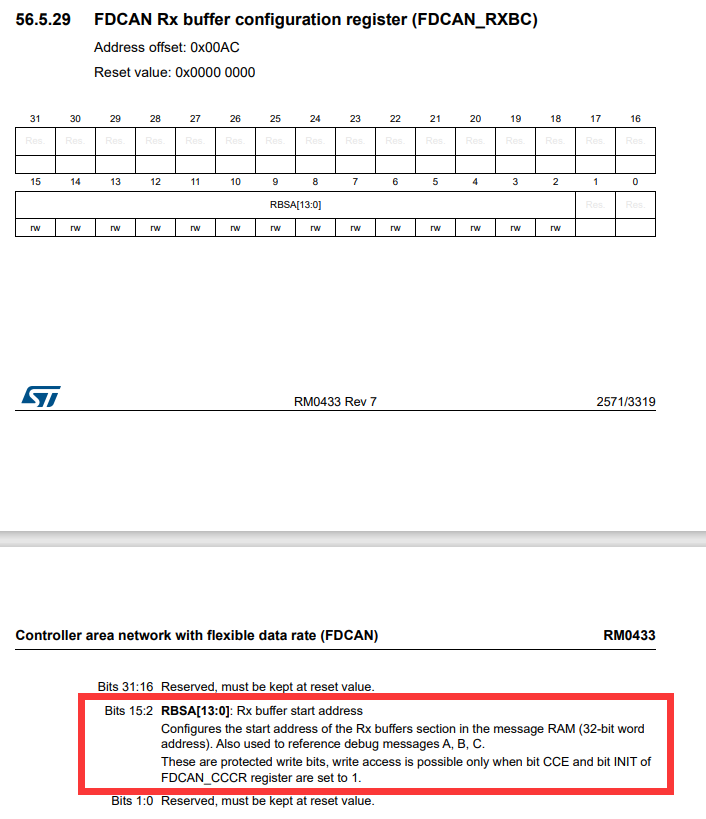

local FDCAN1_RXBC = FDCAN1_BASE + 0x0AC --/*!< FDCAN Rx Buffer Configuration register, Address offset: 0x0AC */

local FDCAN1_RXF1C = FDCAN1_BASE + 0x0B0 --/*!< FDCAN Rx FIFO 1 Configuration register, Address offset: 0x0B0 */

local FDCAN1_RXF1S = FDCAN1_BASE + 0x0B4 --/*!< FDCAN Rx FIFO 1 Status register, Address offset: 0x0B4 */

local FDCAN1_RXF1A = FDCAN1_BASE + 0x0B8 --/*!< FDCAN Rx FIFO 1 Acknowledge register, Address offset: 0x0B8 */

local FDCAN1_RXESC = FDCAN1_BASE + 0x0BC --/*!< FDCAN Rx Buffer/FIFO Element Size Configuration register, Address offset: 0x0BC */

local FDCAN1_TXBC = FDCAN1_BASE + 0x0C0 --/*!< FDCAN Tx Buffer Configuration register, Address offset: 0x0C0 */

local FDCAN1_TXFQS = FDCAN1_BASE + 0x0C4 --/*!< FDCAN Tx FIFO/Queue Status register, Address offset: 0x0C4 */

local FDCAN1_TXESC = FDCAN1_BASE + 0x0C8 --/*!< FDCAN Tx Buffer Element Size Configuration register, Address offset: 0x0C8 */

local FDCAN1_TXBRP = FDCAN1_BASE + 0x0CC --/*!< FDCAN Tx Buffer Request Pending register, Address offset: 0x0CC */

local FDCAN1_TXBAR = FDCAN1_BASE + 0x0D0 --/*!< FDCAN Tx Buffer Add Request register, Address offset: 0x0D0 */

local FDCAN1_TXBCR = FDCAN1_BASE + 0x0D4 --/*!< FDCAN Tx Buffer Cancellation Request register, Address offset: 0x0D4 */

local FDCAN1_TXBTO = FDCAN1_BASE + 0x0D8 --/*!< FDCAN Tx Buffer Transmission Occurred register, Address offset: 0x0D8 */

local FDCAN1_TXBCF = FDCAN1_BASE + 0x0DC --/*!< FDCAN Tx Buffer Cancellation Finished register, Address offset: 0x0DC */

local FDCAN1_TXBTIE = FDCAN1_BASE + 0x0E0 --/*!< FDCAN Tx Buffer Transmission Interrupt Enable register, Address offset: 0x0E0 */

local FDCAN1_TXBCIE = FDCAN1_BASE + 0x0E4 --/*!< FDCAN Tx Buffer Cancellation Finished Interrupt Enable register, Address offset: 0x0E4 */

local FDCAN1_RESERVED62 = FDCAN1_BASE + 0x0E8 --/*!< Reserved, 0x0E8 - 0x0EC */

local FDCAN1_TXEFC = FDCAN1_BASE + 0x0F0 --/*!< FDCAN Tx Event FIFO Configuration register, Address offset: 0x0F0 */

local FDCAN1_TXEFS = FDCAN1_BASE + 0x0F4 --/*!< FDCAN Tx Event FIFO Status register, Address offset: 0x0F4 */

local FDCAN1_TXEFA = FDCAN1_BASE + 0x0F8 --/*!< FDCAN Tx Event FIFO Acknowledge register, Address offset: 0x0F8 */

local FDCAN1_RESERVED7 = FDCAN1_BASE + 0x0FC --/*!< Reserved, 0x0FC */

------------------------------------------------------------------------------------

-- FDCAN Message RAM blocks

------------------------------------------------------------------------------------

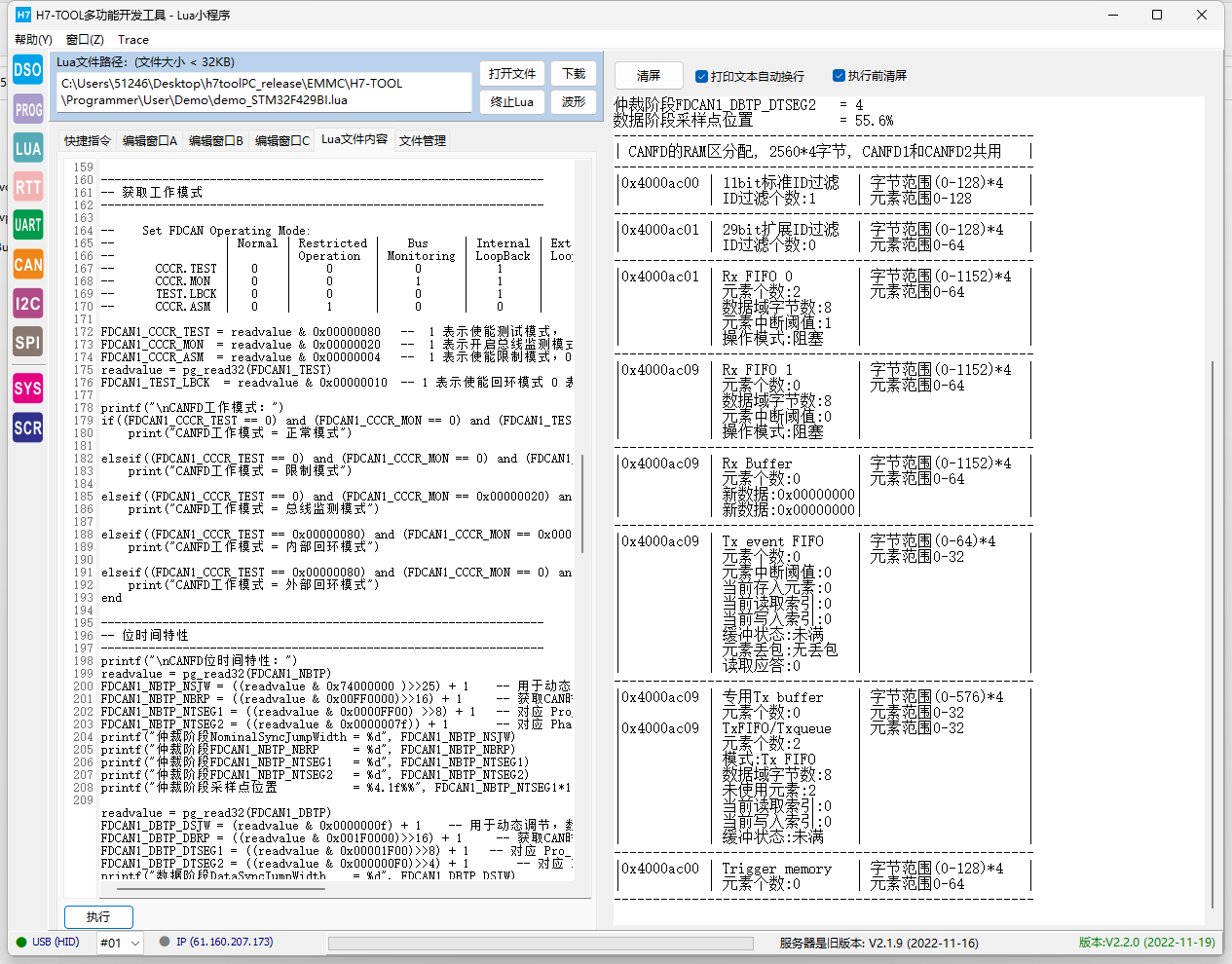

local FDCAN_MsgRamAddress_StandardFilterSA = --/*!< Specifies the Standard Filter List Start Address.

-- This parameter must be a 32-bit word address */

------------------------------------------------------------------------------------

-- FDCAN RAM分配计算

------------------------------------------------------------------------------------

local StartAddress

local readvalue

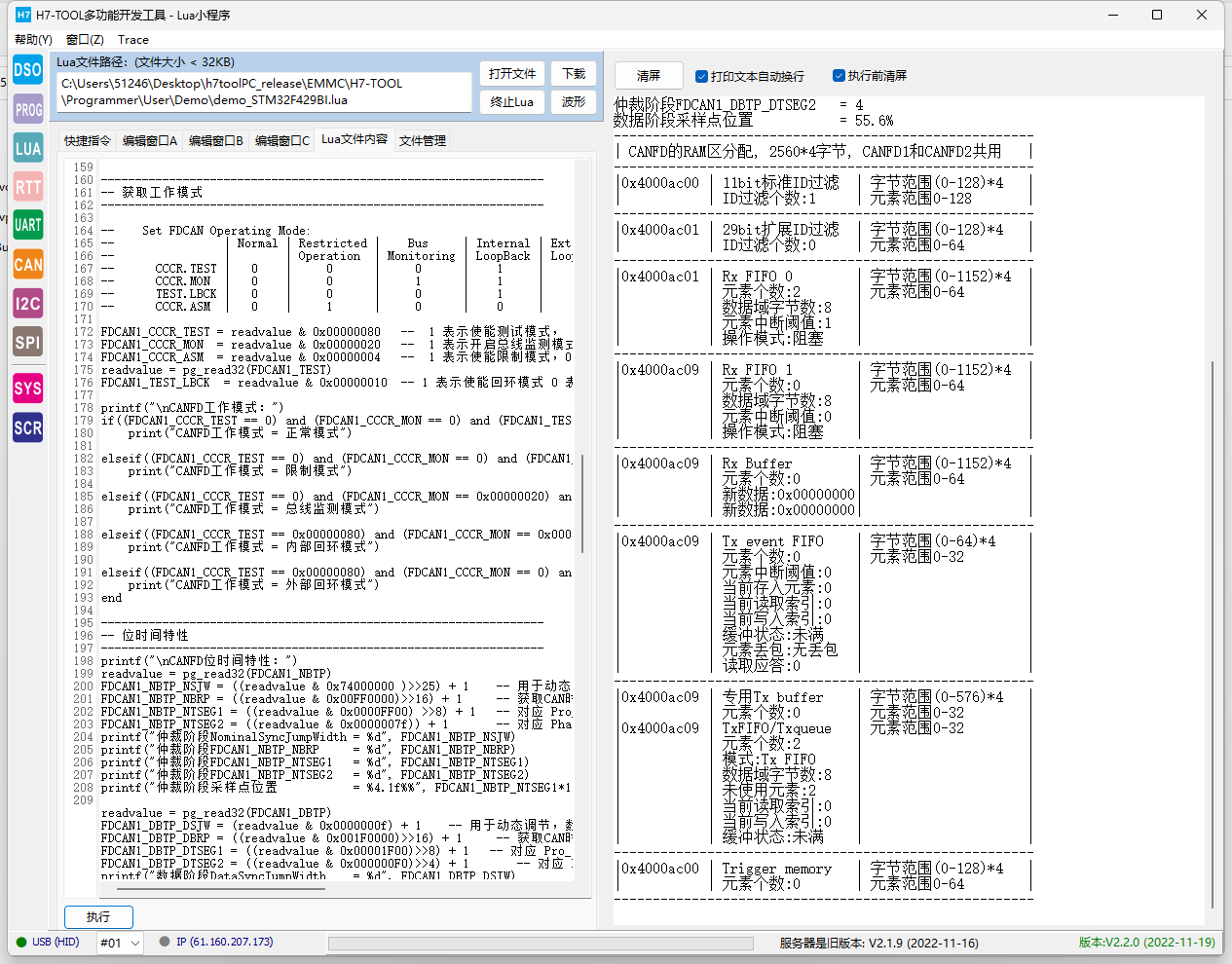

StartAddress = FDCAN1_MessageRAMOffset

pg_init()

readvalue = pg_read32(FDCAN1_SIDFC)

FDCAN1_StandardFilterSA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Standard Filter List Start Address. */

FDCAN1_StandardFilterSANbr = (readvalue & 0x00ff0000) >> 16

readvalue = pg_read32(FDCAN1_XIDFC)

FDCAN1_ExtendedFilterSA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Extended Filter List Start Address */

FDCAN1_ExtendedFilterSANbr = (readvalue & 0x00ff0000) >> 16

readvalue = pg_read32(FDCAN1_XIDFC)

FDCAN1_RxFIFO0SA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Rx FIFO 0 Start Address. */

FDCAN1_RxFIFO0SANbr = (readvalue & 0x007f0000) >> 16

readvalue = pg_read32(FDCAN1_RXF1C)

FDCAN1_RxFIFO1SA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Rx FIFO 1 Start Address.*/

FDCAN1_RxFIFO1SANbr = (readvalue & 0x007f0000) >> 16

readvalue = pg_read32(FDCAN1_RXBC)

FDCAN1_RxBufferSA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Rx Buffer Start Address. */

readvalue = pg_read32(FDCAN1_TXEFC)

FDCAN1_TxEventFIFOSA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Tx Event FIFO Start Address.*/

FDCAN1_TxEventFIFOSANbr = (readvalue & 0x003f0000) >> 16

readvalue = pg_read32(FDCAN1_TXBC)

FDCAN1_TxBufferSA = SRAMCAN_BASE + (readvalue & 0x0000fffc) >> 2 --/*!< Specifies the Tx Buffers Start Address. */

FDCAN1_TxBufferSANbr = (readvalue & 0x003f0000) >> 16 -- Number of dedicated transmit buffers

FDCAN1_TxFIFOQueueNbr = (readvalue & 0x3f000000) >> 24 -- Number of Transmit FIFO/queue size

readvalue = pg_read32(FDCAN1_TXFQS)

FDCAN1_TxFIFOQSA = FDCAN1_TxBufferSA + FDCAN1_TxBufferSANbr * 4; -- /*!< Specifies the Tx FIFO/Queue Start Address. */

--FDCAN1_TTMemorySA; /*!< Specifies the Trigger Memory Start Address. */

--FDCAN1_EndAddress; /*!< Specifies the End Address of the allocated RAM. */

发表于 2023-2-8 02:10:31

发表于 2023-2-8 02:10:31

发表于 2023-2-8 12:04:13

发表于 2023-2-8 12:04:13

楼主

楼主