|

|

楼主 |

发表于 2023-6-27 17:06:17

|

显示全部楼层

__HAL_RCC_GPIOB_CLK_ENABLE();

__HAL_RCC_GPIOC_CLK_ENABLE();

__HAL_RCC_ADC12_CLK_ENABLE(); //使能ADC1/2时钟

GPIO_Initure.Pin = GPIO_PIN_2 | GPIO_PIN_3 | GPIO_PIN_4;

GPIO_Initure.Mode = GPIO_MODE_ANALOG; //模拟

GPIO_Initure.Pull = GPIO_NOPULL; //不带上下拉

HAL_GPIO_Init(GPIOC,&GPIO_Initure); //初始化

GPIO_Initure.Pin = GPIO_PIN_1;

GPIO_Initure.Mode = GPIO_MODE_ANALOG; //模拟

GPIO_Initure.Pull = GPIO_NOPULL; //不带上下拉

HAL_GPIO_Init(GPIOB,&GPIO_Initure); //初始化

RCC->AHB1RSTR|=1<<5; //ADC1/2复位

RCC->AHB1RSTR&=~(1<<5); //复位结束

RCC->D3CCIPR&=~(3<<16); //ADCSEL[1:0]清零

RCC->D3CCIPR|=2<<16; //ADCSEL[1:0]=2,per_ck作为ADC时钟源,默认选择hsi_ker_ck作为per_ck,频率:64Mhz

ADC12_COMMON->CCR|= (11<<18); //PRESC[3:0],输入时钟256分频,即adc_ker_ck=per_ck/256=64/256=250k(不能超过36Mhz)

ADC1->CR=0; //CR寄存器清零,DEEPPWD清零,从深度睡眠唤醒.

ADC1->CR|=1<<28; //ADVREGEN=1,使能ADC稳压器

delay_ms(10); //等待稳压器启动完成,约10us,这里延时大一点,没关系.

ADC1->CR|= 0<<8; //BOOST=0,

ADC1->CFGR |= (1<<13); //循环转换模式

ADC1->CFGR|=1<<12; //OVRMOD=1,复写模式(DR寄存器可被复写)

ADC1->CFGR&=~(3<<10); //EXTEN[1:0]=0,软件触发

ADC1->CFGR&=~(7<<2); //RES[2:0]位清零 16位AD

ADC1->CFGR|=1<<2; //RES[2:0]=1,14位分辨率(0,16位;1,14位;2,12位;3,10位;4,8位.)

ADC1->CFGR|=3<<0; //使能DMA循环模式

ADC1->CFGR2&=~((u32)15<<28);//LSHIFT[3:0]=0,不左移,数据右对齐.

ADC1->CFGR2&=~((u32)0X3FF<<16);//OSR[9:0]=0,不使用过采样

ADC1->CR&=~((u32)1<<30); //ADCALDIF=0,校准单端转换通道

ADC1->CR|=1<<16; //ADCALLIN=1,线性校准

ADC1->CR|=(u32)1<<31; //开启校准

while(ADC1->CR&((u32)1<<31));//等待校准完成

ADC1->SQR1&=~(0XF<<0); //L[3:0]清零

ADC1->SQR1|=0<<0; //L[3:0]=0,1个转换在规则序列中 也就是只转换规则序列1

//设置通道4的采样时间

ADC1->SMPR1 &=~(7<<(12)); //通道采样时间清空

//ADC1->SMPR1 |= (6 << 12); //通道4 8.5个周期,提高采样时间可以提高精确度 8.5 + 7.5 = 16

ADC1->SMPR1 |= (2 << 12); //通道4 8.5个周期,提高采样时间可以提高精确度 8.5 + 7.5 = 16

ADC1->CR|=1<<0; //开启AD转换器

delay_ms(20);

ADC1->PCSEL|=1<<4; //ADC转换通道预选择 ADC12_INP4

//设置转换序列

ADC1->SQR1&=~(0X1F<<6*1); //规则序列1通道清零

ADC1->SQR1|= 4<<6*1; //设置规则序列1的转换通道为ch

ADC1->CR|=1<<2; //启动规则转换通道

RCC->AHB1ENR|=1<<1; //DMA2时钟使能

RCC->D3AMR|=1<<0; //DMAMUX时钟使能

while(DMA2_Stream6->CR&0X01);//等待DMA2_Stream6可配置

DMAMUX1_Channel14->CCR=9; //DMA2_Stream6的通道选择: 9,即AD1对应的通道

DMA2->HIFCR|=0X3D<<16; //清空通道6上所有中断标志

DMA2_Stream6->FCR=0X0000021;//设置为默认值

DMA2_Stream6->PAR=(u32)&ADC1->DR;//外设地址为:ADC1->DR

DMA2_Stream6->M0AR=(u32)buf0;//内存1地址

DMA2_Stream6->NDTR=num; //暂时设置长度为

DMA2_Stream6->CR=0; //先全部复位CR寄存器值

DMA2_Stream6->CR|=0<<6; //外设到存储器模式

DMA2_Stream6->CR|=1<<8; //循环模式

DMA2_Stream6->CR|=0<<9; //外设非增量模式

DMA2_Stream6->CR|=1<<10; //存储器增量模式

DMA2_Stream6->CR|=(u16)width<<11;//外设数据长度:16位/32位

DMA2_Stream6->CR|=(u16)width<<13;//存储器数据长度:16位/32位

DMA2_Stream6->CR|=1<<16; //中等优先级

DMA2_Stream6->CR|=0<<18; //非双缓冲模式

DMA2_Stream6->CR|=0<<21; //外设突发单次传输

DMA2_Stream6->CR|=0<<23; //存储器突发单次传输

DMA2_Stream6->CR|=0<<25;

DMA2_Stream6->FCR&=~(1<<2); //不使用FIFO模式

DMA2_Stream6->FCR&=~(3<<0); //无FIFO 设置

DMA2_Stream6->CR|=1<<4; //开启传输完成中断

MY_NVIC_Init(0,0,DMA2_Stream6_IRQn,2);

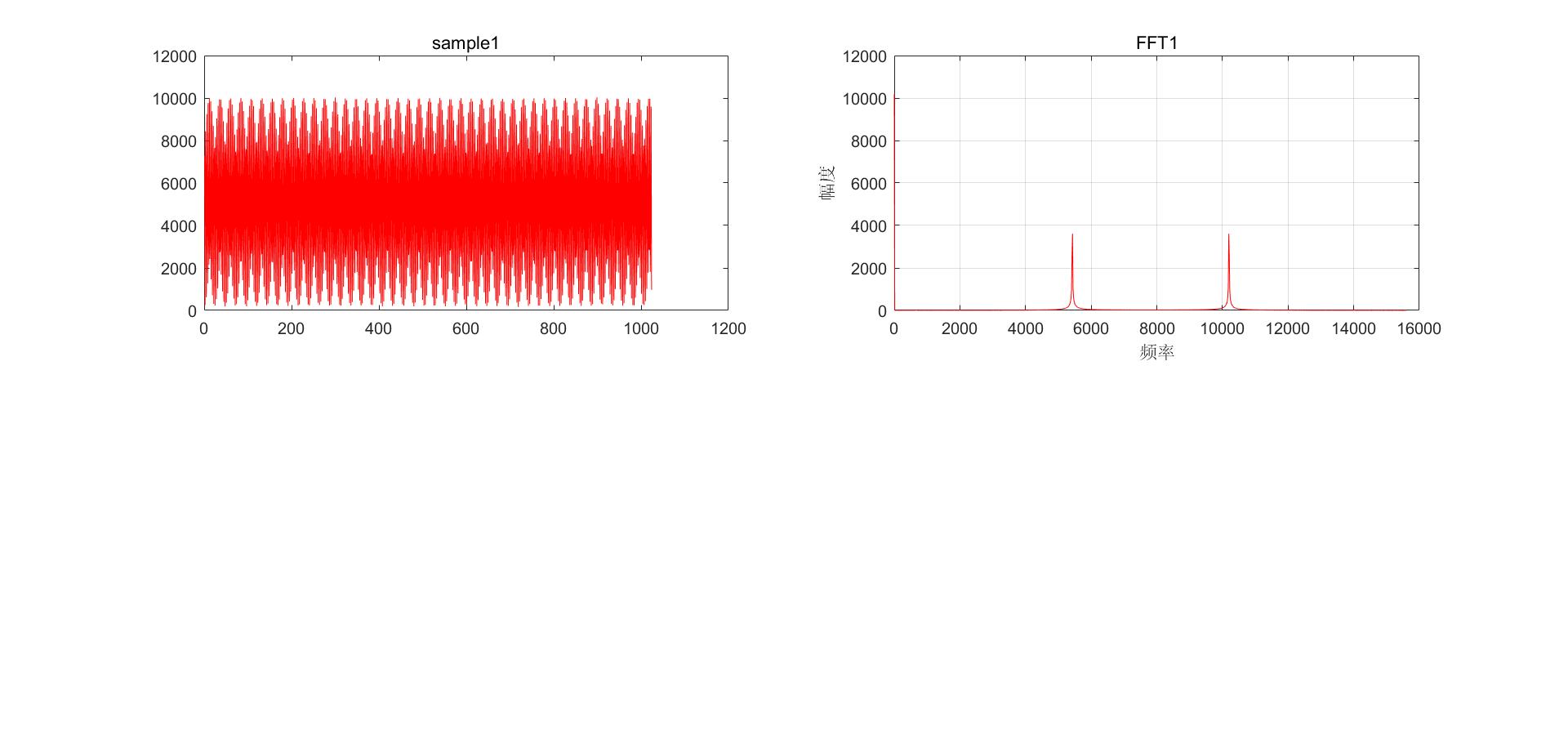

这是AD和DMA设置代码

|

|

发表于 2023-6-26 20:49:30

发表于 2023-6-26 20:49:30

发表于 2023-6-27 08:23:15

发表于 2023-6-27 08:23:15

楼主

楼主