|

|

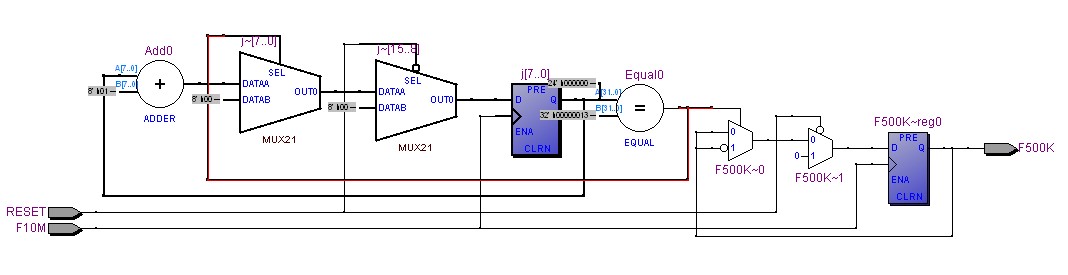

设计一个简单的1/40分频。

module verilog_prj(RESET,F10M,F500K);

input F10M,RESET;

output F500K;

reg F500K;

reg [7:0] j;

always @(posedge F10M)

if(!RESET) //低电平复位。

begin

F500K <= 0;

j <= 7'd0;

end

else

begin

if(j==19) // 对计数器进行判断,以确定F500K 信号是否反转。

begin

j <= 7'd0;

F500K <= ~F500K;

end

else

j <= j + 1'b1;

end

endmodule

测试模块

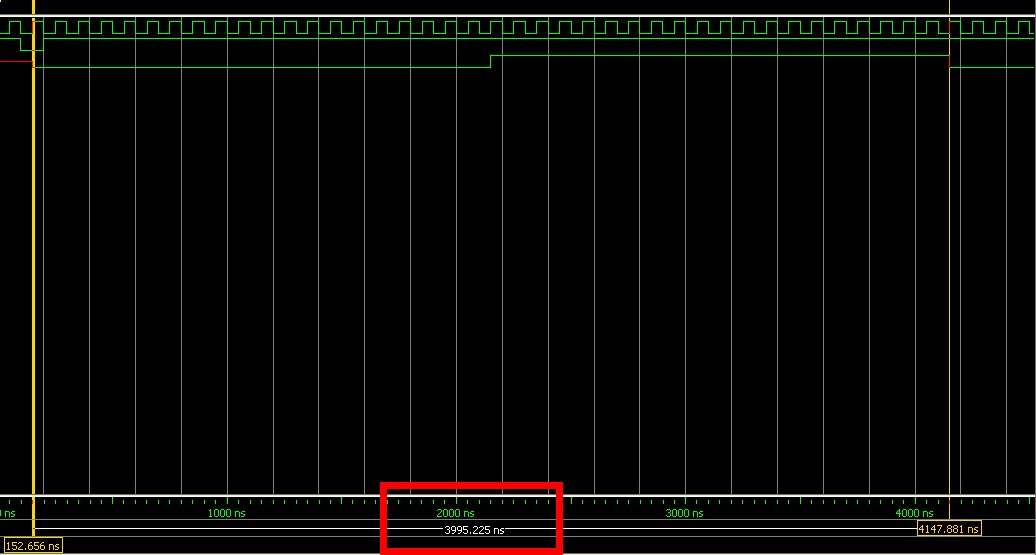

`timescale 1 ns/ 1 ps

module verilog_prj_vlg_tst();

// test vector input registers

reg F10M;

reg RESET;

// wires

wire F500K;

// assign statements (if any)

verilog_prj i1 (

// port map - connection between master ports and signals/registers

.F10M(F10M),

.F500K(F500K),

.RESET(RESET)

);

always #50 F10M = ~ F10M;

initial

begin

RESET=1;

F10M=0;

#100 RESET=0;

#100 RESET=1;

#10000 $stop;

end

endmodule |

|

发表于 2013-1-30 09:34:09

发表于 2013-1-30 09:34:09

楼主

楼主