|

|

楼主 |

发表于 2021-8-13 09:12:29

|

显示全部楼层

static void DM9K_CtrlLinesConfig(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

/* ê1ÄüFSMCê±Öó */

RCC_AHB3PeriphClockCmd(RCC_AHB3Periph_FSMC, ENABLE);

/* ê1Äü GPIOê±Öó */

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOD | RCC_AHB1Periph_GPIOE | RCC_AHB1Periph_GPIOG, ENABLE);

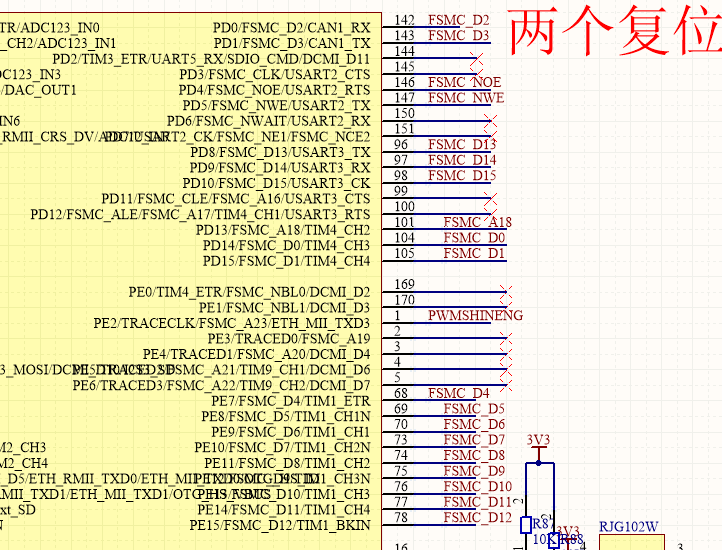

/* éèÖÃ PD.00(D2), PD.01(D3), PD.04(NOE), PD.05(NWE), PD.08(D13), PD.09(D14),

PD.10(D15), PD.14(D0), PD.15(D1) Îa¸′óÃíÆíìêä3ö */

GPIO_PinAFConfig(GPIOD, GPIO_PinSource0, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource1, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource4, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource5, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource8, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource9, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource10, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource14, GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOD, GPIO_PinSource15, GPIO_AF_FSMC);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_4 | GPIO_Pin_5 |

GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_14 |

GPIO_Pin_15;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;

GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL;

GPIO_Init(GPIOD, &GPIO_InitStructure);

/* éèÖÃ PE.07(D4), PE.08(D5), PE.09(D6), PE.10(D7), PE.11(D8), PE.12(D9), PE.13(D10),

PE.14(D11), PE.15(D12) Îa¸′óÃíÆíìêä3ö */

GPIO_PinAFConfig(GPIOE, GPIO_PinSource4 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource5 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource7 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource8 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource9 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource10 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource11 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource12 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource13 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource14 , GPIO_AF_FSMC);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource15 , GPIO_AF_FSMC);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 |

GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 |

GPIO_Pin_15;

GPIO_Init(GPIOE, &GPIO_InitStructure);

/* éèÖà PD.13(A18 (RS)) Îa¸′óÃíÆíìêä3ö */

GPIO_PinAFConfig(GPIOD, GPIO_PinSource13, GPIO_AF_FSMC);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13;

GPIO_Init(GPIOD, &GPIO_InitStructure);

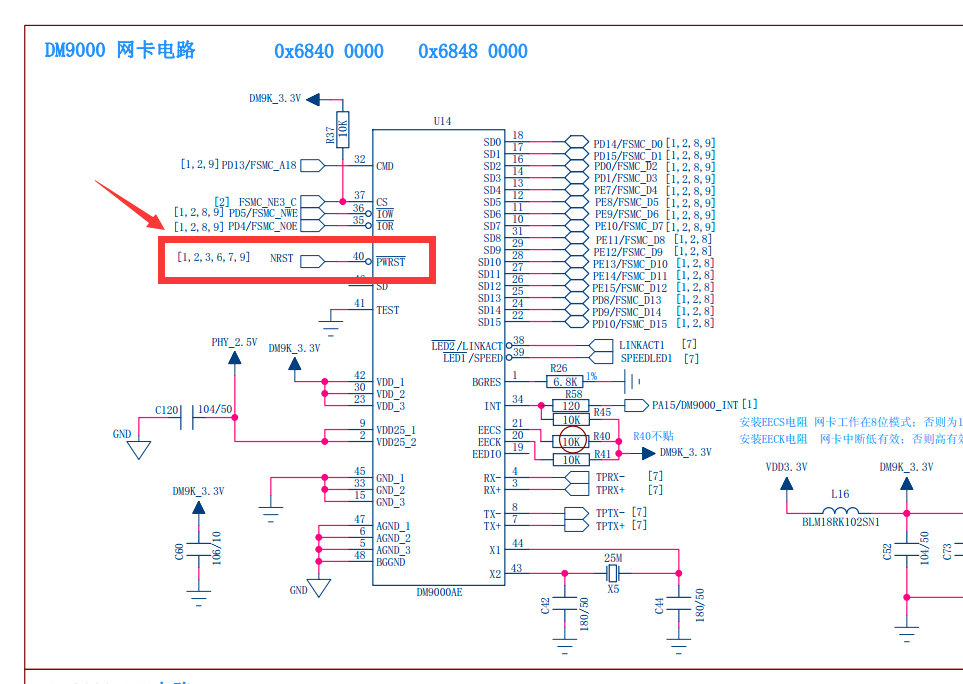

/* éèÖà PG10 (CS)) Îa¸′óÃíÆíìêä3ö */

GPIO_PinAFConfig(GPIOG, GPIO_PinSource10, GPIO_AF_FSMC);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10;

GPIO_Init(GPIOG, &GPIO_InitStructure);

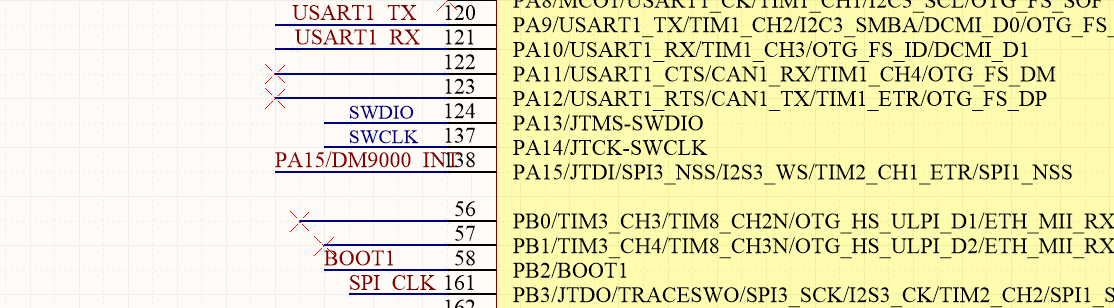

/* PA15 êÇDM9000_INTÖD¶Ïêäèë¿ú(±¾3ìDòÎ′ê1óÃ) */

}

static void DM9K_FSMCConfig(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

FSMC_NORSRAMTimingInitTypeDef p;

/*-- FSMC Configuration ------------------------------------------------------*/

/*----------------------- SRAM Bank 3 ----------------------------------------*/

/*-- FSMC Configuration ------------------------------------------------------*/

p.FSMC_AddressSetupTime = 6; /* éèÖÃÎa2»á3ö′í; 3Õy3£ */

p.FSMC_AddressHoldTime = 2;

p.FSMC_DataSetupTime = 4; /* éèÖÃÎa13ö′í£¬2Õy3£ */

p.FSMC_BusTurnAroundDuration = 8;

p.FSMC_CLKDivision = 0;

p.FSMC_DataLatency = 0;

p.FSMC_AccessMode = FSMC_AccessMode_A;

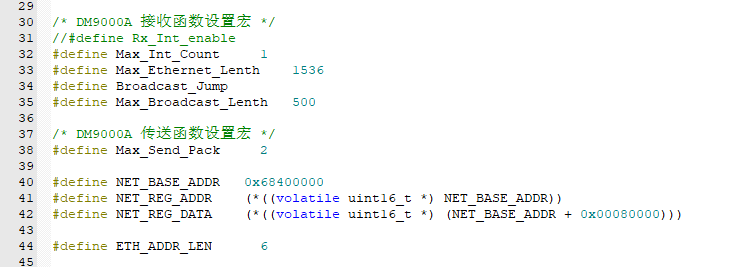

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM3;

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM; // FSMC_MemoryType_PSRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &p;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &p;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

/*!< Enable FSMC Bank1_SRAM3 Bank */

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM3, ENABLE);

}

|

|

发表于 2021-8-8 15:39:47

发表于 2021-8-8 15:39:47

发表于 2021-8-9 12:19:49

发表于 2021-8-9 12:19:49

楼主

楼主