|

|

发表于 2022-2-16 22:45:25

|

显示全部楼层

发表于 2022-2-16 22:45:25

|

显示全部楼层

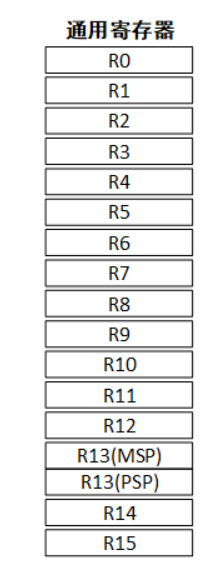

《ARM过程调用约定文档》 (Arm Architecture Procedure Call Standard, AAPCS) 里面定义了很多 ARM 体系结构软/硬件接口会涉及到的术语和概念,其中对 core registers 的功能、分配和ABI层面对行为做了很详细的定义,其中 {r0-r7} 在调用过程中分为低位寄存器和高位寄存器。

低位寄存器属于 caller-save registers,高位寄存器属于 callee-save registers。所以在函数调用发生/上下文切换时,都可以看到子过程跳转前的上下文会负责保存好 {r0-r3} 的上下文。

而高位寄存器作为 callee save context,其上下文状态需要由被调用的函数负责保存和恢复。

C编译器在编译单个函数的时候会根据函数内容进行寄存器分配,当被编译的函数需要使用高位寄存器 {r4-r7} 时,编译器会在函数的入口和出口自动插入对应的保存和恢复上下文的语句 (push/pop)。

Callee-save registers

Are registers that a called procedure must preserve. To preserve a callee-save register, the called procedure would normally either not use the register at all, or store the register to the stack during procedure entry and re-load it from the stack during procedure exit.

Caller-save registers

Are registers that a called procedure need not preserve. If the calling procedure requires their values to be preserved, it must store and reload them itself. The first four registers r0-r3 (a1-a4) are used to pass argument values into a subroutine and to return a result value from a function. They may also be used to hold intermediate values within a routine (but, in general, only between subroutine calls). A subroutine must preserve the contents of the registers r4-r8, r10, r11 and SP (and r9 in PCS variants that designate r9 as v6).

这类底层体系结构相关的问题,一般都可以通过查阅体系结构参考手册、调用约定手册和权威指南得到答案。

我自己经常查阅的资料,从指令集定义到架构实现到软件接口,层次逐渐提升,分别是:

1. IHI0042J, AAPCS

2. DDI0403E, v7m 体系结构参考手册

3. DDI0489F, cortex-m7 架构参考手册

4. DUI0553, cortex-m7 用户设计指南

5. Cortex-M4 权威指南

|

|

发表于 2022-2-16 14:01:08

发表于 2022-2-16 14:01:08

发表于 2022-2-16 14:32:37

发表于 2022-2-16 14:32:37

楼主

楼主 这就去看看汇编

这就去看看汇编