频源,帧率可高达几百帧。其实大家可以发现,市面上关于CameraLink视频输入案例的较多,但公开的CameraLink视频输出案例极少,这在较大程度上阻碍了客户新产品研发进度。

我们收集众多客户关于CameraLink的需求后,为解决客户的视频开发痛点,加快客户产品开发速度,故推出本篇CameraLink OUT案例,下面就一起来看下案例的详细介绍吧!

1.案例功能

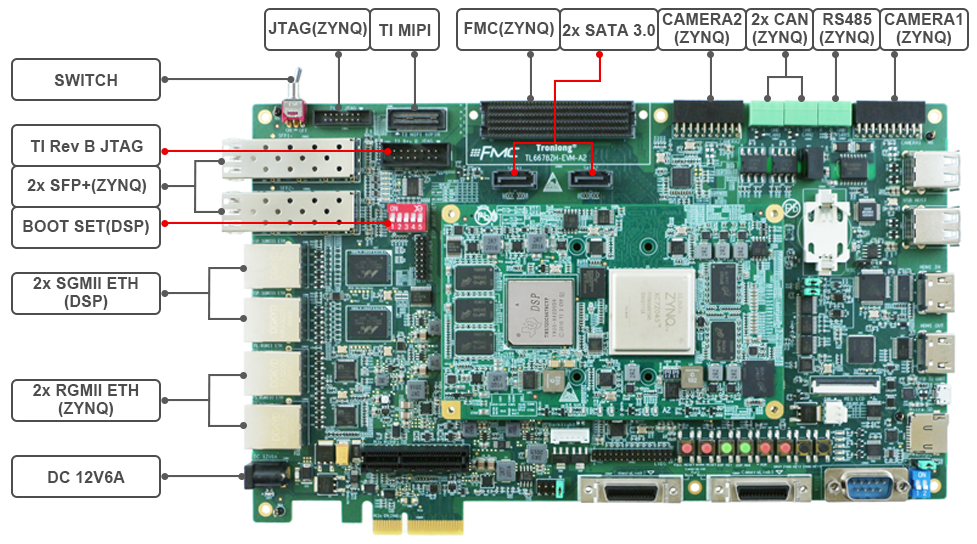

演示平台:TL6678ZH-EVM(C6678+Zynq-7045/7100)评估板

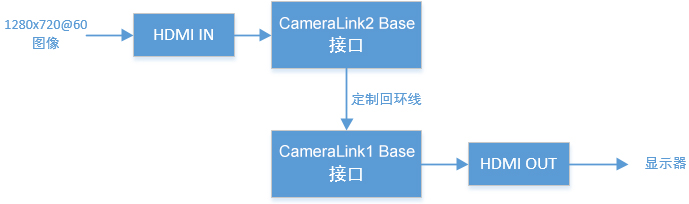

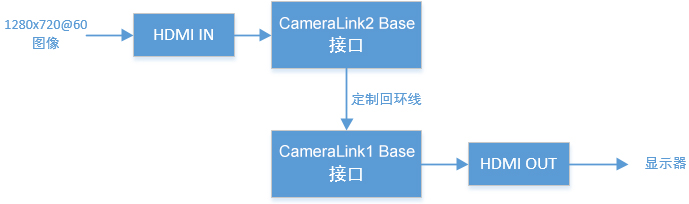

案例功能:本案例作用是验证CameraLink接口在Base模式下的视频输出功能。评估板通过HDMI IN接口进行720P60的视频采集,并通过CameraLink2接口将采集到的视频进行输出,再通过CameraLink1接口接入来自CameraLink2接口的视频输出信号,最后通过HDMI OUT接口进行视频输出。

图 3

2.操作说明

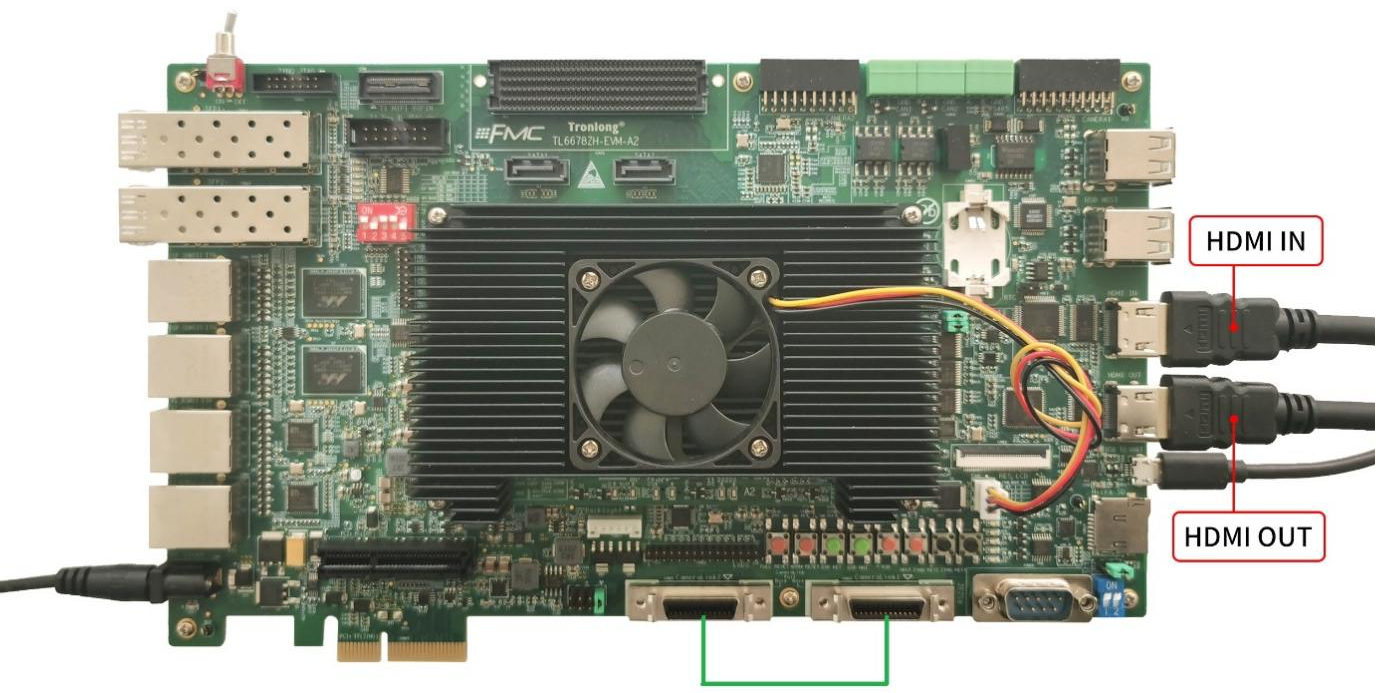

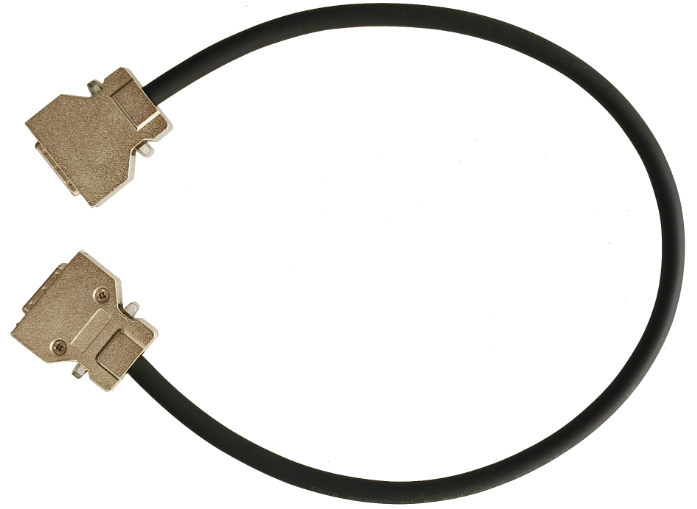

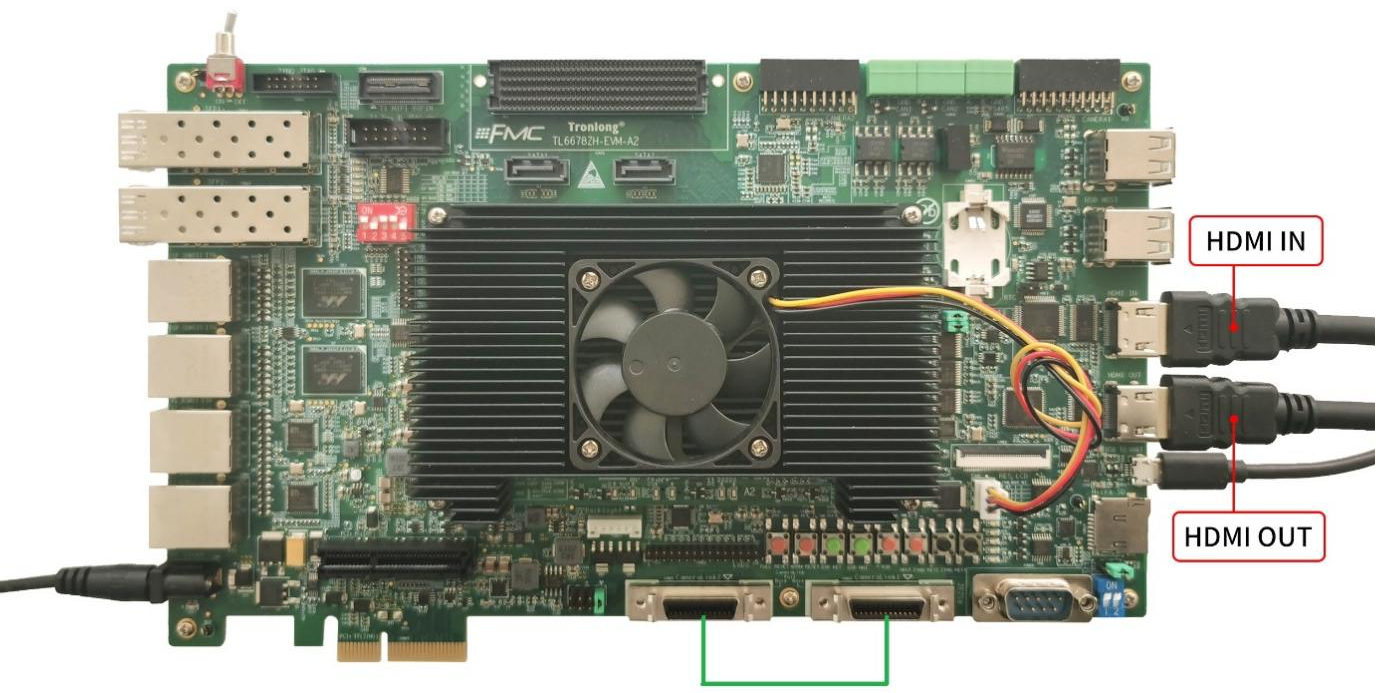

准备一台拥有HDMI OUT接口的PC机(例如笔记本),通过HMDI数据线将PC机HDMI OUT接口连接至评估板的HDMI IN接口,PC机HDMI OUT接口用作图像输出。通过HMDI数据线将一台HDMI显示屏连接至评估板的HDMI OUT接口,HDMI显示屏用作图像显示。使用创龙科技的CameraLink回环线(型号:MDR-MDR 0.5m)连接评估板的CameraLink1、CameraLink2接口。

图 4

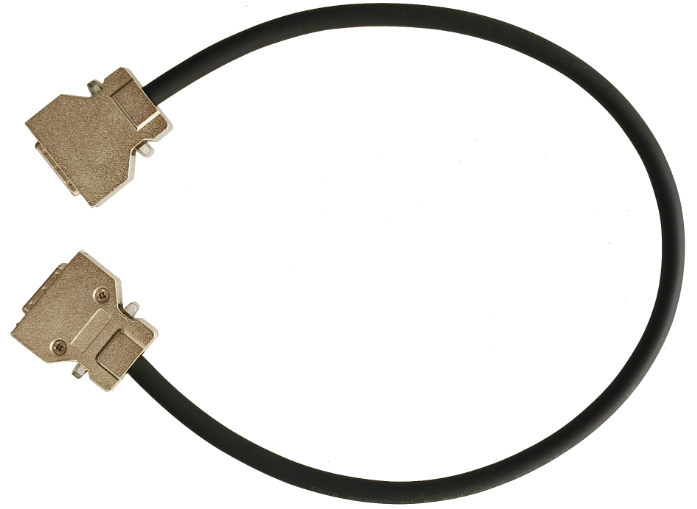

图 5 CameraLink回环线

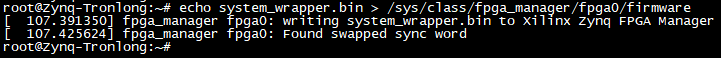

将本案例的PL端.bin格式可执行文件复制到"/lib/firmware/"目录下,并将PL端可执行文件重命名为system_wrapper.bin,然后执行如下命令加载PL端可执行文件。

Target#echo

system_wrapper.bin > /sys/class/fpga_manager/fpga0/firmware

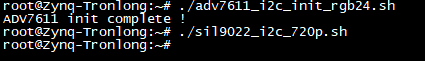

图 6

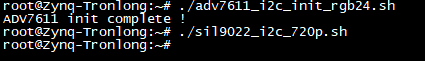

将案例"sw\linux_system\image\"目录下所有脚本文件拷贝至评估板文件系统,并执行如下命令。

Target#./adv7611_i2c_init_rgb24.sh

Target#./sil9022_i2c_720p.sh

图 7

在PC机的显卡设置(或图形属性)中,按照下图设置HDMI分辨率为1280 x 720、刷新率为60pHz,即可看到HDMI显示屏输出PC机输出的原始图像。

图 8

图 9

3. Vivado工程说明

打开BLOCK DESIGN开发界面,可查看Vivado工程。

图 10

4.模块配置

4.1 lvds_n_x_7to1_sdr_tx模块

本案例使用lvds_n_x_7to1_sdr_tx模块将HDMI IN接口输入的并行数据转化成差分数据,LVDS使用SDR模式,在时钟的单边沿传输数据。

lvds_n_x_7to1_sdr_tx模块开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《xapp585-lvds-source-synch-serdes-clock-multiplication.pdf》。lvds_n_x_7to1_sdr_tx模块源码文件为Vivado工程"cameralink_loopback.srcs\sources_1\imports\hdl\lvds_n_x_7to1_sdr_tx.v",具体配置说明如下。

1.配置N(通道数量)为3对应Full模式,配置N为1则对应Base模式。配置D为4,表示“每个通道的数据差分对数量为4”。

Base模式:单通道,每通道数据差分对为4组,需1个连接器。

Medium模式:双通道,每通道数据差分对为4组,需2个连接器。

Full模式:三通道,每通道数据差分对为4组,需2个连接器。

图 11

4.2 lvds_n_x_1to7_sdr_rx模块

本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink1接口输入的差分视频数据转化成并行视频数据。

lvds_n_x_1to7_sdr_rx模块开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《xapp585-lvds-source-synch-serdes-clock-multiplication.pdf》。lvds_n_x_1to7_sdr_rx模块源码文件为Vivado工程"cameralink_loopback.srcs\sources_1\imports\hdl\lvds_n_x_1to7_sdr_rx.v",具体配置说明如下。

(1)delay_refclk_in接入由PS端输出的200MHz参考时钟。

图 12

(1)配置N(通道数量)为3对应Full模式,配置N为1则对应Base模式。配置X为4,表示“每个通道的数据差分对数量为4”。

Base模式:单通道,每通道数据差分对为4组,需1个连接器。

Medium模式:双通道,每通道数据差分对为4组,需2个连接器。

Full模式:三通道,每通道数据差分对为4组,需2个连接器。

图 13

发表于 2021-4-20 11:23:33

发表于 2021-4-20 11:23:33