|

1.1 问题描述 期望代码顺序为: x=42; Ok= 1; 但编译优化后: Ok=1; X=42; 1.2 解决方法使用memory barriers技术,即让编译器知道一定要按这个顺序给出汇编代码。 在MDK里面,就是__dsb(unsigned int), __isb(unsigned int)。 然后我翻到了第8章,但是不理解表里面的Ordered Accessed是什么意思? arm汇编手册第8章摘要Memory barriers

Memory barriers ensure specific ordering properties between memory accesses. For more details on memory

barriers, see ARM ARM [v7 section A3.8.3]. The intrinsics in this section are available for all targets. They may be

no-ops (i.e. generate no code, but possibly act as a code motion barrier in compilers) on targets where the

relevant instructions do not exist, but only if the property they guarantee would have held anyway. On targets

where the relevant instructions exist but are implemented as no-ops, these intrinsics generate the instructions.

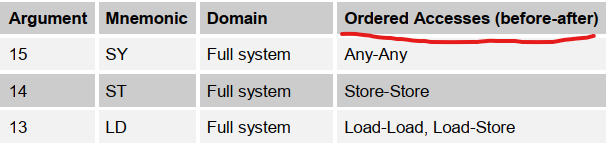

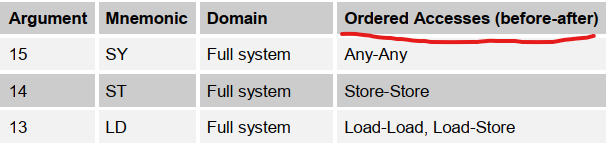

The memory barrier intrinsics take a numeric argument indicating the scope and access type of the barrier, as

shown in the following table. (The assembler mnemonics for these numbers, as shown in the table, are not

available in the intrinsics.) The argument should be an integral constant expression within the required range –

see section 4.3.1.

Examples

In this example, process P1 makes some data available to process P2 and sets a flag to indicate this.

P1:

value = x;

/* issue full-system memory barrier for previous store:

setting of flag is guaranteed not to be observed before

write to value */

__dmb(14);

flag = true;

P2:

/* busy-wait until the data is available */

while (!flag) {}

/* issue full-system memory barrier: read of value is guaranteed

not to be observed by memory system before read of flag */

__dmb(15);

use value;

|

发表于 2021-1-3 17:54:10

发表于 2021-1-3 17:54:10

发表于 2021-1-4 10:34:10

发表于 2021-1-4 10:34:10

楼主

楼主