|

|

楼主 |

发表于 2022-3-15 07:59:17

|

显示全部楼层

SPI技术参数:

硬件CS支持 (主机从机都可以用)

分布到芯片的很多引脚上 (看Pinout就知道)

支持多种SPI模式 (TI/NI/摩托罗拉)

自带FIFO (深度8 * 32B)

支持4B – 16B传输帧 (但是需要考虑FIFO问题)

DMA/IRQ/突发传输支持 (正常标配)

可以用作从机 (但是没有例子)

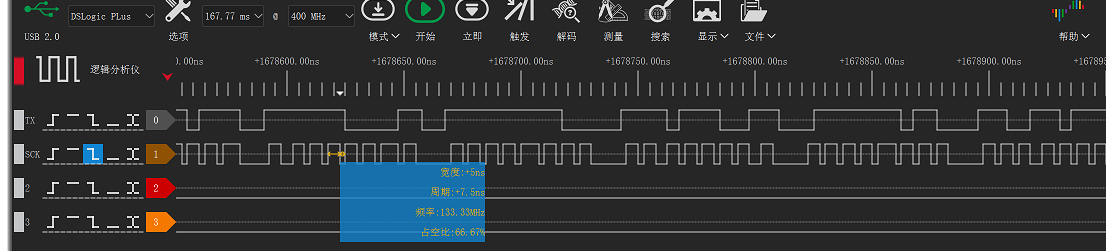

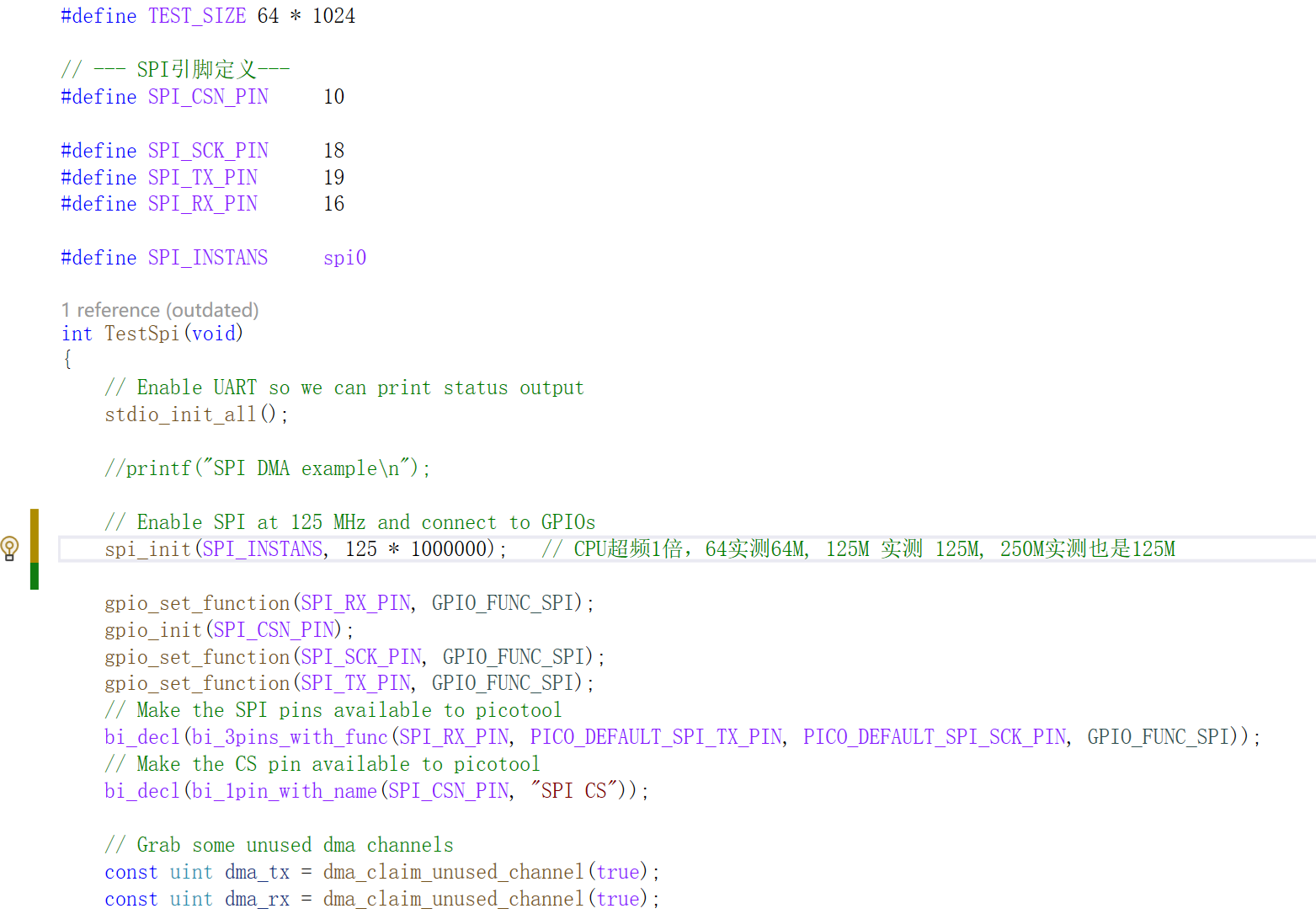

频率支持(主机):Fperi/65024 ~ Fperi/2 (在标准125MHz下,即约2kHz到约75MHz)

频率支持(从机):Fper/65024 ~ Fperi/12 (在标准125MHz下,即约12kHz到约10.4MHz)

2组SPI (都可以自由用)

PL022 公版IP (ARM白送IP,树莓派自己没设计.)

When configured as a master, the clock to the attached slaves is derived from a divided-down version of SSPCLK through

the previously described prescaler operations. The master transmit logic successively reads a value from its transmit

FIFO and performs parallel to serial conversion on it. Then, the serial data stream and frame control signal, synchronized

to SSPCLKOUT, are output through the SSPTXD pin to the attached slaves. The master receive logic performs serial to

parallel conversion on the incoming synchronous SSPRXD data stream, extracting and storing values into its receive FIFO,

for subsequent reading through the APB interface.

当配置为主服务器时,附加从服务器的时钟通过前面描述的预调用器操作从SSPCLK的划分版本派生出来。

主传输逻辑从其传输FIFO中依次读取一个值,并对其执行并行的串行转换。然后,串行数据流和帧控制

信号通过SSPTXD引脚输出到附加的从端。主接收逻辑对传入的同步SSPRXD数据流执行串行到并行的转

换,将值提取并存储到其接收FIFO中,以便随后通过APB接口读取。

When configured as a slave, the SSPCLKIN clock is provided by an attached master and used to time its transmission and

reception sequences. The slave transmit logic, under control of the master clock, successively reads a value from its

transmit FIFO, performs parallel to serial conversion, then outputs the serial data stream and frame control signal through

the slave SSPTXD pin. The slave receive logic performs serial to parallel conversion on the incoming SSPRXD data stream,

extracting and storing values into its receive FIFO, for subsequent reading through the APB interface.

当配置为从属服务器时,该快速切换时钟由一个附加的主服务器提供,并用于计时其传输和接收序列。从

发送逻辑在主时钟的控制下,从其发送FIFO中依次读取一个值,并行进行串行转换,然后通过从SSPTXD

引脚输出串行数据流和帧控制信号。从接收逻辑对传入的SSPRXD数据流进行串行到并行的转换,将值提

取并存储到其接收的FIFO中,

|

|

发表于 2022-3-14 23:34:54

发表于 2022-3-14 23:34:54

楼主

楼主 发表于 2022-3-15 08:47:54

发表于 2022-3-15 08:47:54