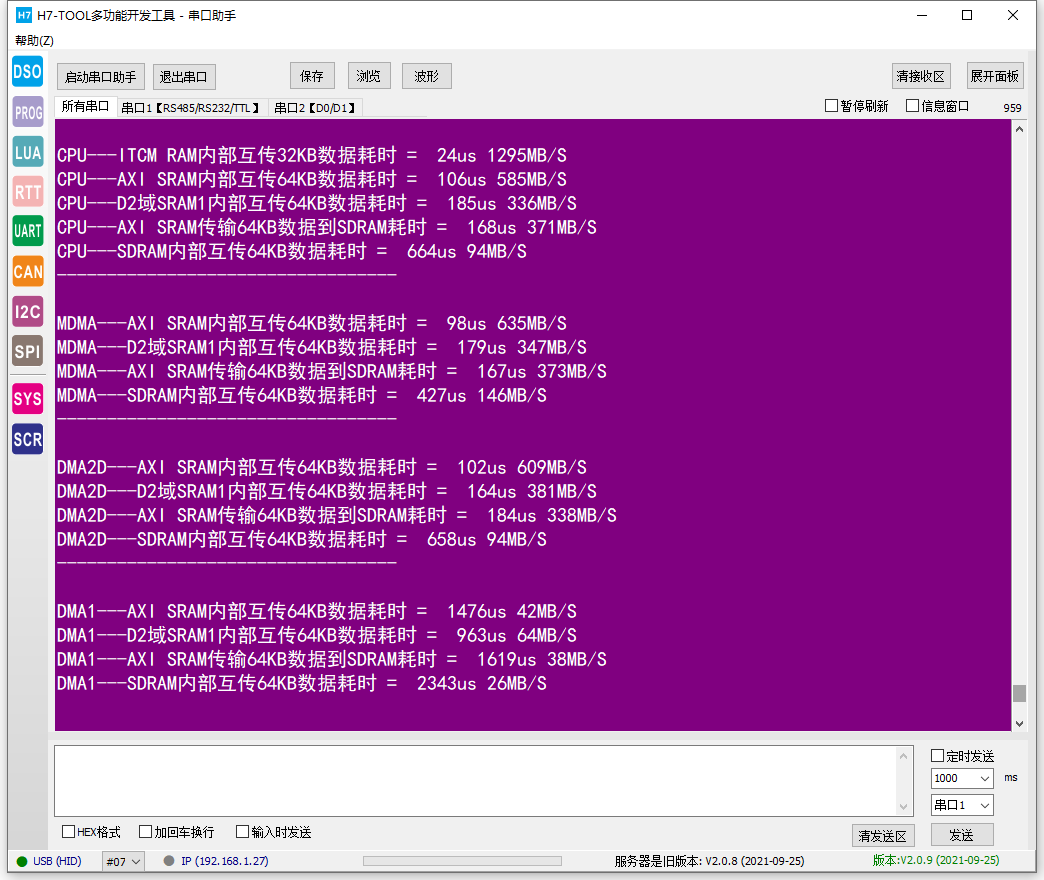

ОЙ§ВтЪдSTM32H750ЕФDMA1ЁЂDMA2ПЩвддкШчЯТХфжУЯТЃЌЪЕЯжЮоSRAMзмЯпОКељЕФЬѕМўЯТЃЌ6ИіAHBзмЯпЪБжгвЛДЮЕФSRAMЕНGPIOЕФЪ§ОнАсдЫЁЃ

[C] ДПЮФБОВщПД ИДжЦДњТы

__HAL_RCC_DMA1_CLK_ENABLE();

DMA_Handle.Instance = DMA1_Stream1;

DMA_Handle.Init.Request = DMA_REQUEST_GENERATOR0;

DMA_Handle.Init.Direction = DMA_MEMORY_TO_PERIPH;

DMA_Handle.Init.PeriphInc = DMA_PINC_DISABLE;

DMA_Handle.Init.MemInc = DMA_MINC_ENABLE;

DMA_Handle.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD;

DMA_Handle.Init.MemDataAlignment = DMA_MDATAALIGN_WORD;

DMA_Handle.Init.Mode = DMA_CIRCULAR;

DMA_Handle.Init.Priority = DMA_PRIORITY_LOW;

DMA_Handle.Init.FIFOMode = DMA_FIFOMODE_ENABLE;

DMA_Handle.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_HALFFULL; // DMA_FIFO_THRESHOLD_1QUARTERFULL;

DMA_Handle.Init.MemBurst = DMA_MBURST_SINGLE;

DMA_Handle.Init.PeriphBurst = DMA_PBURST_SINGLE;

зіЕН6ИіжмЦкЭъГЩвЛДЮДЋЪфЕФЙиМќдкгкDMAЕФFIFOЩшжУЃЌЪЙгУFIFOКѓЃЌгІИУЪЧНЕЕЭСЫDMAЖдSRAMзмЯпЕФашЧѓЃЌЫѕЖЬСЫвЛДЮДЋЪфЕФЪБжгашЧѓЁЃ

дкНћжЙFIFOЪБЃЌашвЊ9ИіЪБжгВХФмЮШЖЈДЅЗЂвЛДЮДЋЪфЁЃ

ЖјЧвЖдFIFOЕФДЅЗЂуажЕВЛФмЩшжУЮЊFULL |

ЗЂБэгк 2023-2-14 19:20:30

ЗЂБэгк 2023-2-14 19:20:30

ТЅжї

ТЅжї

ЗЂБэгк 2023-2-15 02:11:16

ЗЂБэгк 2023-2-15 02:11:16