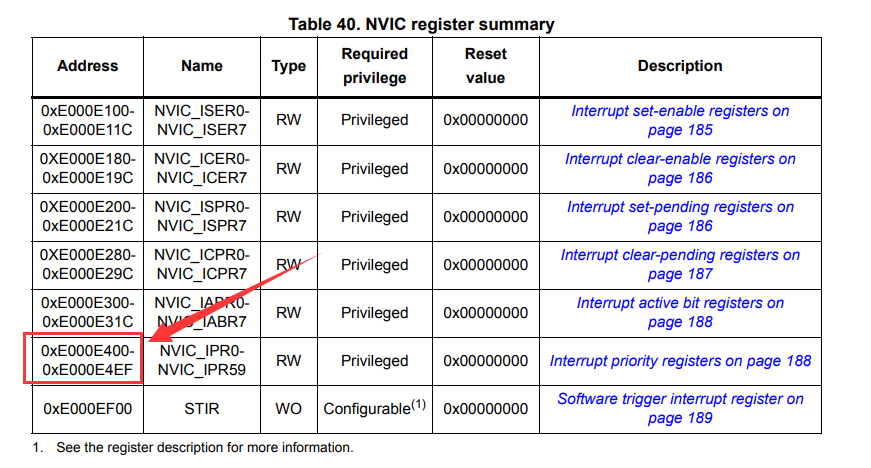

首次看这里很容易不太理解,实际上这里有个隐含的问题,中断向量序号表前16个是系统中断。后面才是用户中断。

实际自己实现操作了下,才意识到这个问题,开始还以为是个bug:

#define portNVIC_IP_REGISTERS_OFFSET_16 ( 0xE000E3F0 )

static const volatile uint8_t * const pcInterruptPriorityRegisters = ( uint8_t * ) portNVIC_IP_REGISTERS_OFFSET_16;

ucCurrentPriority = pcInterruptPriorityRegisters[ ulCurrentInterrupt ]; -- 比较考验细节

[C] 纯文本查看 复制代码 void vPortValidateInterruptPriority( void )

{

uint32_t ulCurrentInterrupt;

uint8_t ucCurrentPriority;

/* Obtain the number of the currently executing interrupt. */

ulCurrentInterrupt = vPortGetIPSR();

/* Is the interrupt number a user defined interrupt? */

if( ulCurrentInterrupt >= portFIRST_USER_INTERRUPT_NUMBER )

{

/* Look up the interrupt's priority. */

ucCurrentPriority = pcInterruptPriorityRegisters[ ulCurrentInterrupt ];

/* The following assertion will fail if a service routine (ISR) for

an interrupt that has been assigned a priority above

configMAX_SYSCALL_INTERRUPT_PRIORITY calls an ISR safe FreeRTOS API

function. ISR safe FreeRTOS API functions must *only* be called

from interrupts that have been assigned a priority at or below

configMAX_SYSCALL_INTERRUPT_PRIORITY.

Numerically low interrupt priority numbers represent logically high

interrupt priorities, therefore the priority of the interrupt must

be set to a value equal to or numerically *higher* than

configMAX_SYSCALL_INTERRUPT_PRIORITY.

Interrupts that use the FreeRTOS API must not be left at their

default priority of zero as that is the highest possible priority,

which is guaranteed to be above configMAX_SYSCALL_INTERRUPT_PRIORITY,

and therefore also guaranteed to be invalid.

FreeRTOS maintains separate thread and ISR API functions to ensure

interrupt entry is as fast and simple as possible.

The following links provide detailed information:

[url]http://www.freertos.org/RTOS-Cortex-M3-M4.html[/url]

[url]http://www.freertos.org/FAQHelp.html[/url] */

configASSERT( ucCurrentPriority >= ucMaxSysCallPriority );

}

/* Priority grouping: The interrupt controller (NVIC) allows the bits

that define each interrupt's priority to be split between bits that

define the interrupt's pre-emption priority bits and bits that define

the interrupt's sub-priority. For simplicity all bits must be defined

to be pre-emption priority bits. The following assertion will fail if

this is not the case (if some bits represent a sub-priority).

If the application only uses CMSIS libraries for interrupt

configuration then the correct setting can be achieved on all Cortex-M

devices by calling NVIC_SetPriorityGrouping( 0 ); before starting the

scheduler. Note however that some vendor specific peripheral libraries

assume a non-zero priority group setting, in which cases using a value

of zero will result in unpredictable behaviour. */

configASSERT( ( portAIRCR_REG & portPRIORITY_GROUP_MASK ) <= ulMaxPRIGROUPValue );

}

|

发表于 2023-7-6 01:12:06

发表于 2023-7-6 01:12:06

楼主

楼主

发表于 2024-3-14 11:49:00

发表于 2024-3-14 11:49:00