|

|

http://www.elecfans.com/article/83/116/2012/20120428269548.html

引言

转换效率促使FPGA系统设计师从线性稳压器转向使用开关模式直流-直流转换器。虽然开关模式直流-直流转换器能够显着提高效率,但却需要更复杂的结构设计,更多的部件数量和更大的覆盖区;更为明显的是,对高速输入/输出单元来说,开关模式直流-直流转换器就等于噪声源。

本文描述了开关模式直流-直流转换器的各种噪声分量,同时说明PowerSoC如何将各分量降至最低。本文也进一步用设计示例来说明PowerSoC如何令高速输入/输出单元具有与线性稳压器媲美,甚至更优越的性能。

降压型直流-直流转换器简单模型

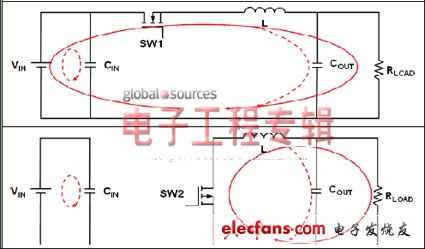

一对MOSFET开关、电感器,以及输入和输出滤波电容即可组成一个简易的同步开关模式直流-直流转换器模型。图1为转换周期中的转换器及其相关的直流和交流电流通路。当SW1 闭合时(SW2开启),电流从电源流经电感器到达负载,输入和输出滤波电容实现高频交流电流的"分流".当SW2闭合时(SW1开启),电感器储存的电能在转换周期的后半段为负载提供电流。开启和闭合开关的动作以及高频交流电流的流动都会产生噪声。

图1:同步降压型直流-直流转换器简化模型之完整转换周期。红色实线表示"直流"电流的流动方向,而红色虚线表示高频交流电流的流动方向。

直流-直流噪声关键分量和降噪策略

降压型直流-直流转换器有效地将直流电压"分成"交流电压,然后转换回到伪直流电压。此过程产生了四种不同的噪声:1) 转换器直流输出侧的纹波电压,2) 转换器输入电源侧的纹波电压,3) 辐射性电磁干扰,和4)传导性电磁干扰。

输出电压纹波

每个被动元件除了本身的基本功能(电阻、电容、电感)外,还具有另外两个寄生元素:如果是电容,即为等效串联电阻 (ESR) 和等效串联电感 (ESL);如果是电阻,则是等效串联电感和等效并联电容。

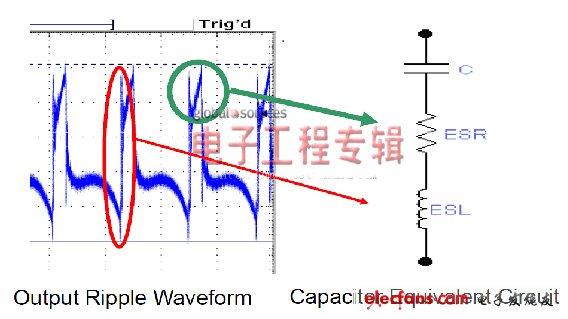

输出纹波是交流纹波电流分流或流经输出滤波电容时的副产物。图2展示了小型的输出滤波电容信号模型,和该模型各成分对输出纹波波形的作用。请注意输出滤波电容的ESL是由PCB引线的寄生电感和转换器的内部寄生电感结合形成。ESL通过感应"振动"产生高频尖峰信号。

图2:输出电压纹波分量和来源

大多数直流-直流转换器供应商的数据表显示了低通滤波纹波的波形,因此通常无法稳定指示给定应用情况中PCB上测量得到的实际纹波。

降噪策略

基本而言,要降低输出纹波可通过减小纹波电流和 / 或降低电容器 的ESR和ESL以及PCB引线的ESL.

●在开关频率较高的一侧操作将降低给定电感值的纹波电流,从而可以使用较小且ESR/ESL较低的陶瓷电容。但开关频率的升高会增加MOSFET开关的开关损耗,并影响效率。

●将多个电容并联可降低ESR/ESL,就如将电阻并联以降低其合成电阻一样。随着电容个数增加,PCB ESL增加,其效果受到限制,并且将增加转换器的消耗。

●使用小尺寸的滤波元件(电感器和电容)可以减少PCB的长度,从而降低PCB ESL.可惜小尺寸的电感器通常会导致纹波电流较大,但不增加开关频率。

●使用两级滤波,例如在直流-直流输出滤波段和目标负载之间使用铁氧体磁珠和电容。这种方法的缺点在于额外的致损耗元件将影响调压效果,并可能降低效率。

输入电压纹波

随着SW1 MOSFET打开和闭合,电流从电源(VIN)流出,形成近似矩形的脉冲波形。上升和下降时间非常快,大约几毫微秒。

与由输出滤波电容和PCB引线ESL产生的输出纹波相似,输入滤波电容ESR和ESL,以及电源PCB引线ESL产生输入纹波。然而,随着电流时间比(di/dt)的变化增大,输入电流纹波幅度要大的多。因此,PCB电感的影响更为重要,而输入滤波电容必须耐受更高的RMS电流。又大又快的开关电流也是传导性和辐射性EMI(稍后将探讨)的主要来源。

降噪策略

●与输出滤波电容一样,在开关频率较高的一侧操作将可以使用较小且ESR/ESL较低的陶瓷输入滤波电容。同样应注意开关损耗将变大。

●将输入滤波回路中的寄生电感降至最低。这主要通过将滤波电容尽可能靠近直流-直流转换器,以及尽可能短且宽的PCB引线来实现。通常不得将输入滤波电容安装在PCB的对边且通过vias与直流-直流转换器连接,否则会将大量电感引入电流回路中。

辐射性EMI

●又大又快的开关电流流经输入交流电流回路会产生辐射性EMI.如电磁场课程所述,环形天线的辐射效率是回路半径相对于辐射波长的函数。

●公式1列出了环形天线辐射产生的功率与半径r和波长λ的关系;h是自由空间常数。请注意回路半径存在r8关系,而波长存在λ4的关系。因此,在频率较高的一侧操作的显着优点是可使用较小尺寸的元件,以缩小输入电流回路半径。

降噪策略

减少输入交流电流回路的半径。通过在较高频率一侧开关以使用较小尺寸的陶瓷滤波电容,即可达到此目的。同样应注意,如上文所述,开关频率越高,开关损耗也越大。

传导性EMI

传导性EMI有两个主要来源:首先是输入电压干线产生的快速开关输入电流,它会造成电源纹波(差模)和接地弹跳(共模)EMI;其次则是在电路板PCB引线上的电感器磁通泄漏耦合。

降噪策略

●使用大小合适的输入滤波电容供应或过滤高频交流电源,以便尽可能降低电源干线上的电流。

●将输入交流电流回路中的寄生电感和 ESL 降至最低。这可以通过在开关频率较高的一侧操作实现,这样就可以使用低 ESL 的陶瓷电容器,从而缩小回路半径。需要再次强调的是开关频率越高,开关损耗也越高。

●让输入滤波电容的 PCB 引线尽可能短且宽以降低引线电感。

●使用屏蔽式电感器以降低磁漏。

PowerSoC作为降噪策略

Enpirion于2004年推出全球第一个PowerSoC .PowerSoC在单个IC套件中集成了完整的直流 - 直流转换器,包括控制器、栅极驱动器、MOSFET开关、高频去耦,以及最重要的电感器。大多数 PowerSoC 只需要输入和输出滤波电容,因此整个解决方案既简单又轻巧。

●使用专用的深亚微米高频 LDMOS 既可实现低开关损耗,又能集成整套的控制、驱动和开关元件。低开关损耗可以实现高开关频率,例如 5MHz.

●高密度、高磁导率、小体积的磁性元件可以实现最低的交流损耗和低直流电阻。小体积的磁性元件和磁结构具有自屏蔽特性,可以降低磁漏。高开关频率则允许使用尺寸非常小的电感器。

●高开关频率还允许使用小型的输入和输出滤波电容,这样一来,可以缩小输入和输出交流回路的尺寸,从而降低纹波和 EMI.

●套件布线经过设计可进一步缩小输入和输出交流滤波回路的半径,从而尽可能降低辐射性和传导性 EMI 以及纹波。

●套件设计包括射频技术,旨在尽可能降低内部电路元件内的寄生阻抗以保持套件内的高频交流电源。

PowerSoC结果与离散实现方案

图3–6展示了 PowerSoC 与离散式直流 - 直流转换器实现方案的对比结果。

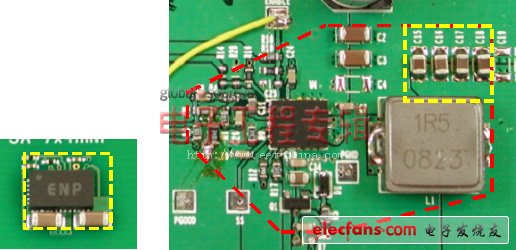

图3:典型4A大小的转换器解决方案区域对比。PowerSoC(左图)的输入和输出交流电流回路非常小,相当于典型离散式实现方案尺寸的1/7.

黄色虚线方框表示PowerSoC尺寸和离散式直流-直流转换器的对比结果。

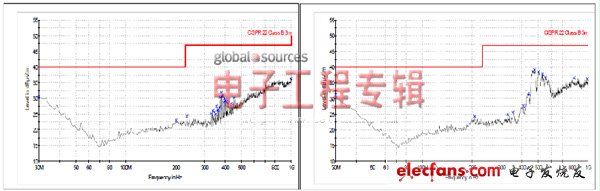

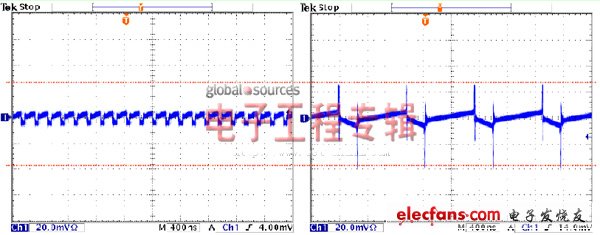

图4 owerSoC(左图)与离散式直流-直流转换器实现方案(右图)的输出纹波电压对比。二者使用相同的设备和技术在供应商评估板上测量纹波。测量带宽为500MHz. owerSoC(左图)与离散式直流-直流转换器实现方案(右图)的输出纹波电压对比。二者使用相同的设备和技术在供应商评估板上测量纹波。测量带宽为500MHz.

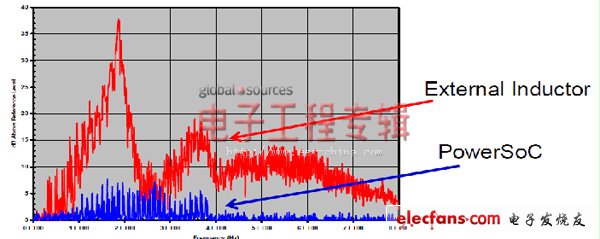

图5:辐射性EMI测量结果;CISPR22 B等级3m.左图为PowerSoC,右图为离散式实现方案,均在供应商评估板上测量得出。

图6:输入接地端子上测量的传导性干扰

采用Enpirion PowerSoC的供电Rocket IO应用实例

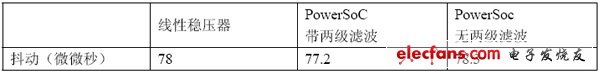

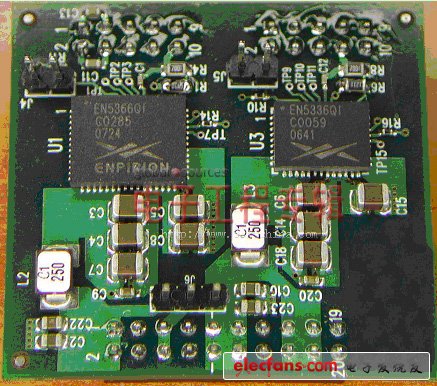

设计制造的子板插到Virtex 5开发板上(图7)。对采用Enpirion装置驱动的开发板和线性稳压器执行同样的抖动测量。分别测量Enpirion PowerSoC有两级滤波和无两级滤波的效果。抖动测量结果如表1所示。

表1. Rocket IO的抖动测量结果

图7:带Enpirion PowerSoC的子板

结论

对FPGA设计师而言PowerSoC代表强效的新型工具。这种装置能够有效减少从基于线性稳压器的电压转换器向更高效的开关模式转换器转变过程中面临的诸多问题。 PowerSoC具有和线性稳压器相似的覆盖区域,易于设计,同时也拥有开关模式转换器的高效率,却可免去离散式转换器实现方案的噪声和复杂度。 |

|

发表于 2014-10-24 10:47:32

发表于 2014-10-24 10:47:32

owerSoC(左图)与离散式直流-直流转换器实现方案(右图)的输出纹波电压对比。二者使用相同的设备和技术在供应商评估板上测量纹波。测量带宽为500MHz.

owerSoC(左图)与离散式直流-直流转换器实现方案(右图)的输出纹波电压对比。二者使用相同的设备和技术在供应商评估板上测量纹波。测量带宽为500MHz.