|

|

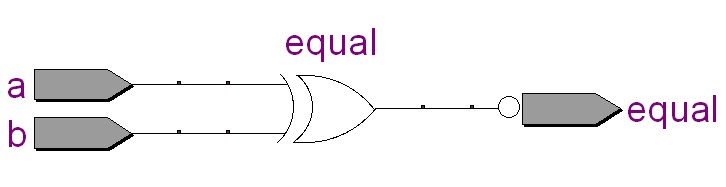

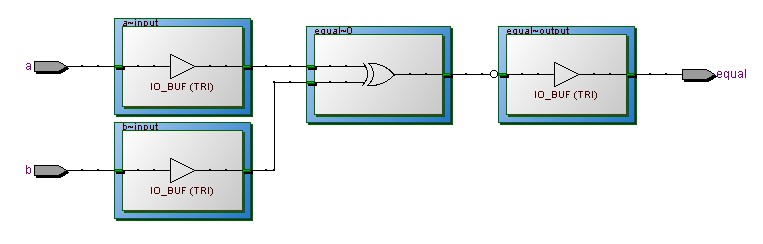

例子非常简单,就是一个简单的比较器。

下面主要看ModelSim的功能仿真和生成的RTL视图和Technology Map视图。

module verilog_prj(equal,a,b);

input a,b;

output equal;

assign equal=(a==b)? 1'b1:1'b0; //a等于b 时,equal输出为1;a不等于b 时,

//equal输出为0。

endmodule

测试模块程序

`timescale 1 ns/ 1 ns

module verilog_prj_vlg_tst();

// test vector input registers

reg a;

reg b;

// wires

wire equal;

// assign statements (if any)

verilog_prj i1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.equal(equal)

);

initial

begin

a=0;

b=0;

#100 a=0; b=1;

#100 a=1; b=1;

#100 a=1; b=0;

#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

end

endmodule

|

|

发表于 2013-1-29 14:47:27

发表于 2013-1-29 14:47:27

楼主

楼主