|

|

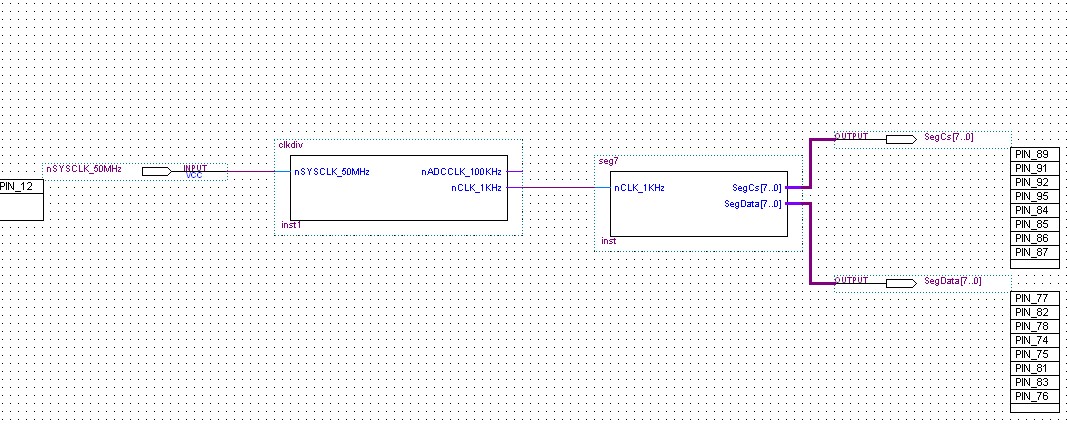

说明: 这里的数码管驱动比较简单,以后的程序尽量采用模块的形式进行设计

提供时钟分频的部分

module clkdiv

(

nSYSCLK_50MHz,

nADCCLK_100KHz,

nCLK_1KHz

);

input nSYSCLK_50MHz;

output nADCCLK_100KHz;

output nCLK_1KHz;

reg nADCCLK_100KHz, nCLK_1KHz;

reg[7:0] rCount;

reg[14:0] rCount1ms;

/*

**********************************************

generate 100ksps for adc

**********************************************

*/

always@(negedge nSYSCLK_50MHz)

begin

if(rCount <= 8'd250)

rCount <= rCount + 1'b1;

else

begin

rCount <= 8'd0;

nADCCLK_100KHz <= ~nADCCLK_100KHz;

end

end

/*

**********************************************

generate 100Hz for 7SEG

**********************************************

*/

always@(posedge nSYSCLK_50MHz)

begin

if(rCount1ms > 15'd25000)

begin

nCLK_1KHz <= ~nCLK_1KHz;

rCount1ms <= 15'd0;

end

else

rCount1ms <= rCount1ms + 1'b1;

end

endmodule

数码管扫描

module seg7

(

nCLK_1KHz, //scan clk

SegCs, //seg cs

SegData //seg data

);

input nCLK_1KHz;

output[7:0] SegCs;

output[7:0] SegData;

/* used for seg */

reg[7:0] SegCs;

reg[7:0] SegData;

reg[3:0] number;

reg[9:0] counter;

reg[7:0] segdata;

/*

**********************************************

Data convert to 7SEG

**********************************************

*/

function[7:0] leddata; //返回一个8位的数字

input[3:0] datain;

begin

case(datain)

4'd0: leddata=8'b11000000;//0

4'd1: leddata=8'b11111001;//1

4'd2: leddata=8'b10100100;//2

4'd3: leddata=8'b10110000;//3

4'd4: leddata=8'b10011001;//4

4'd5: leddata=8'b10010010;//5

4'd6: leddata=8'b10000010;//6

4'd7: leddata=8'b11111000;//7

4'd8: leddata=8'b10000000;//8

4'd9: leddata=8'b10010000;//9

4'ha: leddata = 8'h88;

4'hb: leddata = 8'h83;

4'hc: leddata = 8'hc6;

4'hd: leddata = 8'ha1;

4'he: leddata = 8'h86;

4'hf: leddata = 8'h8e;

default:leddata=8'bzzzz_zzzz;

endcase

end

endfunction

/*

**********************************************

7SEG SACN

**********************************************

*/

always@(posedge nCLK_1KHz)

begin

if(number == 4'd9)

begin

number <= 4'd0;

end

else

begin

number <= number + 1'b1;

case(number)

4'd0: /*adc low 4bit*/

begin

SegData <= leddata(segdata[3:0]);

SegCs <= 8'b11111110;

end

4'd1: /*adc high 4bit*/

begin

SegData <= leddata(segdata[7:4]);

SegCs <= 8'b11111101;

end

4'd2:

begin

SegData <= leddata(4'd5);

SegCs <= 8'b11111011;

end

4'd3:

begin

SegData <= leddata(4'd4);

SegCs <= 8'b11110111;

end

4'd4:

begin

SegData <= leddata(4'd3);

SegCs <= 8'b11101111;

end

4'd5:

begin

SegData <= leddata(4'd2);

SegCs <= 8'b11011111;

end

4'd6:

begin

SegData <= leddata(4'd1);

SegCs <= 8'b10111111;

end

4'd7:

begin

SegData <= leddata(4'd1);

SegCs <= 8'b01111111;

end

endcase

end

end

always@(posedge nCLK_1KHz)

begin

counter <= counter + 1'b1;

if(counter == 10'd1000)

begin

counter <= 10'd0;

if(segdata[3:0] == 9)

begin

segdata[3:0] <= 0;

if (segdata[7:4] == 5)

begin

segdata[7:4] <= 0;

end

else

begin

segdata[7:4] <= segdata[7:4] + 1'b1;

end

end

else

begin

segdata[3:0] <= segdata[3:0] + 1'b1;

end

end

end

endmodule

|

|

发表于 2013-2-3 12:12:16

发表于 2013-2-3 12:12:16

楼主

楼主