|

|

楼主 |

发表于 2013-2-3 12:21:25

|

显示全部楼层

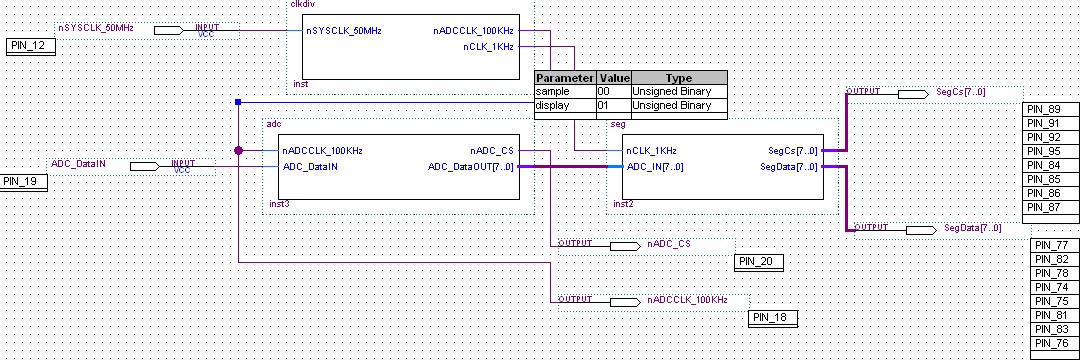

Re:CPLD570实验四:ADC TLC549

module adc

(

nADCCLK_100KHz, //TLC549 clk

ADC_DataIN, //TLC549 data in

nADC_CS, //AD TLC549 cs

ADC_DataOUT //TLC549 data out

);

input ADC_DataIN;

output[7:0] ADC_DataOUT;

output nADC_CS;

input nADCCLK_100KHz;

/* used for ADC */

reg nADC_CS;

reg[3:0] cnt;

reg[7:0] dataout;

reg[7:0] ADC_DataOUT;

/* used for FSM */

reg[1:0] state;

parameter sample = 2'b00,

display = 2'b01;

/*

**********************************************

ADC Program

**********************************************

*/

always@(negedge nADCCLK_100KHz)

begin

case(state)

sample:

begin

nADC_CS <= 1'b0;

dataout[7:0] <= {dataout[6:0], ADC_DataIN};

if(cnt > 4'd7)

begin

cnt <= 4'd0;

state<=display;

end

else

begin

cnt <= cnt + 1'b1;

state <= sample;

end

end

display:

begin

nADC_CS <= 1'b1; //关AD片选

ADC_DataOUT <= dataout;

//得到采集的数据

state<=sample;

end

default: state<=display;

endcase

end

endmodule |

|

发表于 2013-2-3 12:15:24

发表于 2013-2-3 12:15:24

楼主

楼主