|

|

发表于 2018-6-12 12:59:02

|

显示全部楼层

发表于 2018-6-12 12:59:02

|

显示全部楼层

这个简单,发给ld文件给你:

/*

* GENERATED FILE - DO NOT EDIT

* (c) Code Red Technologies Ltd, 2008-2013

* (c) NXP Semiconductors 2013-2018

* Generated linker script file for MIMXRT1052xxxxx

* Created from linkscript.ldt by FMCreateLinkLibraries

* Using Freemarker v2.3.23

* MCUXpresso IDE v10.1.1 [Build 606] [2018-01-02] on Apr 25, 2018 5:18:51 PM

*/

GROUP (

libcr_nohost_nf.a

libcr_c.a

libcr_eabihelpers.a

)

MEMORY

{

/* Define each memory region */

BOARD_FLASH (rx) : ORIGIN = 0x60000000, LENGTH = 0x1000000 /* 16M bytes (alias Flash) */

SRAM_DTC (rwx) : ORIGIN = 0x20000000, LENGTH = 0x20000 /* 128K bytes (alias RAM) */

SRAM_ITC (rwx) : ORIGIN = 0x0, LENGTH = 0x20000 /* 128K bytes (alias RAM2) */

SRAM_OC (rwx) : ORIGIN = 0x20200000, LENGTH = 0x40000 /* 256K bytes (alias RAM3) */

BOARD_SDRAM (rwx) : ORIGIN = 0x80000000, LENGTH = 0x2000000 /* 32M bytes (alias RAM4) */

}

/* Define a symbol for the top of each memory region */

__base_BOARD_FLASH = 0x60000000 ; /* BOARD_FLASH */

__base_Flash = 0x60000000 ; /* Flash */

__top_BOARD_FLASH = 0x60000000 + 0x1000000 ; /* 16M bytes */

__top_Flash = 0x60000000 + 0x1000000 ; /* 16M bytes */

__base_SRAM_DTC = 0x20000000 ; /* SRAM_DTC */

__base_RAM = 0x20000000 ; /* RAM */

__top_SRAM_DTC = 0x20000000 + 0x20000 ; /* 128K bytes */

__top_RAM = 0x20000000 + 0x20000 ; /* 128K bytes */

__base_SRAM_ITC = 0x0 ; /* SRAM_ITC */

__base_RAM2 = 0x0 ; /* RAM2 */

__top_SRAM_ITC = 0x0 + 0x20000 ; /* 128K bytes */

__top_RAM2 = 0x0 + 0x20000 ; /* 128K bytes */

__base_SRAM_OC = 0x20200000 ; /* SRAM_OC */

__base_RAM3 = 0x20200000 ; /* RAM3 */

__top_SRAM_OC = 0x20200000 + 0x40000 ; /* 256K bytes */

__top_RAM3 = 0x20200000 + 0x40000 ; /* 256K bytes */

__base_BOARD_SDRAM = 0x80000000 ; /* BOARD_SDRAM */

__base_RAM4 = 0x80000000 ; /* RAM4 */

__top_BOARD_SDRAM = 0x80000000 + 0x2000000 ; /* 32M bytes */

__top_RAM4 = 0x80000000 + 0x2000000 ; /* 32M bytes */

ENTRY(ResetISR)

SECTIONS

{

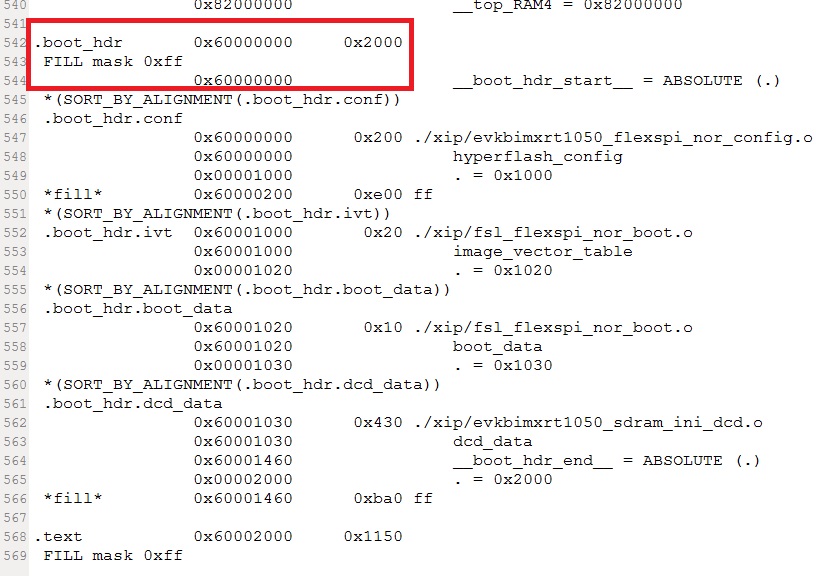

/* Image Vector Table and Boot Data for booting from external flash */

.boot_hdr : ALIGN(4)

{

FILL(0xff)

__boot_hdr_start__ = ABSOLUTE(.) ;

KEEP(*(.boot_hdr.conf))

. = 0x1000 ;

KEEP(*(.boot_hdr.ivt))

. = 0x1020 ;

KEEP(*(.boot_hdr.boot_data))

. = 0x1030 ;

KEEP(*(.boot_hdr.dcd_data))

__boot_hdr_end__ = ABSOLUTE(.) ;

. = 0x2000 ;

} >BOARD_FLASH

/* MAIN TEXT SECTION */

.text : ALIGN(4)

{

FILL(0xff)

__vectors_start__ = ABSOLUTE(.) ;

KEEP(*(.isr_vector))

/* Global Section Table */

__section_table_start = .;

__data_section_table = .;

LONG(LOADADDR(.data));

LONG( ADDR(.data));

LONG( SIZEOF(.data));

LONG(LOADADDR(.data_RAM2));

LONG( ADDR(.data_RAM2));

LONG( SIZEOF(.data_RAM2));

LONG(LOADADDR(.data_RAM3));

LONG( ADDR(.data_RAM3));

LONG( SIZEOF(.data_RAM3));

LONG(LOADADDR(.data_RAM4));

LONG( ADDR(.data_RAM4));

LONG( SIZEOF(.data_RAM4));

__data_section_table_end = .;

__bss_section_table = .;

LONG( ADDR(.bss));

LONG( SIZEOF(.bss));

LONG( ADDR(.bss_RAM2));

LONG( SIZEOF(.bss_RAM2));

LONG( ADDR(.bss_RAM3));

LONG( SIZEOF(.bss_RAM3));

LONG( ADDR(.bss_RAM4));

LONG( SIZEOF(.bss_RAM4));

__bss_section_table_end = .;

__section_table_end = . ;

/* End of Global Section Table */

*(.after_vectors.init_data)

*(.after_vectors.init_bss)

*(.after_vectors.reset)

} >BOARD_FLASH

.text : ALIGN(4)

{

/***

libcr_nohost_nf.a(.text* .rodata .rodata.* .constdata .constdata.*)

libcr_c.a(.text* .rodata .rodata.* .constdata .constdata.*)

libcr_eabihelpers.a(.text* .rodata .rodata.* .constdata .constdata.*)

**/

*startup_mimxrt1052.o(.text* .rodata .rodata.* .constdata .constdata.*)

*system_MIMXRT1052.o(.text* .rodata .rodata.* .constdata .constdata.*)

/***

*fsl_clock.o(.text* .rodata .rodata.* .constdata .constdata.*)

*fsl_semc.o(.text* .rodata .rodata.* .constdata .constdata.*)

*clock_config.o(.text* .rodata .rodata.* .constdata .constdata.*)

*pin_mux.o(.text* .rodata .rodata.* .constdata .constdata.*)

***/

*blue1.o(.text* .rodata .rodata.* .constdata .constdata.*)

*blue2.o(.text* .rodata .rodata.* .constdata .constdata.*)

*blue3.o(.text* .rodata .rodata.* .constdata .constdata.*)

. = ALIGN(4);

} >BOARD_FLASH

/*

* for exception handling/unwind - some Newlib functions (in common

* with C++ and STDC++) use this.

*/

.ARM.extab : ALIGN(4)

{

*(.ARM.extab* .gnu.linkonce.armextab.*)

} > SRAM_ITC AT>BOARD_FLASH

__exidx_start = .;

.ARM.exidx : ALIGN(4)

{

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

} > SRAM_ITC AT>BOARD_FLASH

__exidx_end = .;

_etext = .;

/* DATA section for SRAM_ITC */

.data_RAM2 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM2 = .) ;

KEEP(*(.isr_ramvectors))

*(.after_vectors)

*(.text*)

*(.ramfunc.$RAM2)

*(.ramfunc.$SRAM_ITC)

*(.data.$RAM2*)

*(.data.$SRAM_ITC*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM2 = .) ;

} > SRAM_ITC AT>BOARD_FLASH

/* DATA section for SRAM_OC */

.data_RAM3 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM3 = .) ;

*(.ramfunc.$RAM3)

*(.ramfunc.$SRAM_OC)

*(.data.$RAM3*)

*(.data.$SRAM_OC*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM3 = .) ;

} > SRAM_OC AT>BOARD_FLASH

/* DATA section for BOARD_SDRAM */

.data_RAM4 : ALIGN(4)

{

FILL(0xff)

PROVIDE(__start_data_RAM4 = .) ;

*(.ramfunc.$RAM4)

*(.ramfunc.$BOARD_SDRAM)

*(.data.$RAM4*)

*(.data.$BOARD_SDRAM*)

. = ALIGN(4) ;

PROVIDE(__end_data_RAM4 = .) ;

} > BOARD_SDRAM AT>BOARD_FLASH

/* MAIN DATA SECTION */

.uninit_RESERVED : ALIGN(4)

{

KEEP(*(.bss.$RESERVED*))

. = ALIGN(4) ;

_end_uninit_RESERVED = .;

} > SRAM_DTC

/* Main DATA section (SRAM_DTC) */

.data : ALIGN(4)

{

FILL(0xff)

_data = . ;

*(vtable)

*(.ramfunc*)

*(.data*)

*(.rodata .rodata.* .constdata .constdata.*)

. = ALIGN(4) ;

_edata = . ;

} > SRAM_DTC AT>BOARD_FLASH

/* BSS section for SRAM_ITC */

.bss_RAM2 : ALIGN(4)

{

PROVIDE(__start_bss_RAM2 = .) ;

*(.bss.$RAM2*)

*(.bss.$SRAM_ITC*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM2 = .) ;

} > SRAM_ITC

/* BSS section for SRAM_OC */

.bss_RAM3 : ALIGN(4)

{

PROVIDE(__start_bss_RAM3 = .) ;

*(.bss.$RAM3*)

*(.bss.$SRAM_OC*)

. = ALIGN (. != 0 ? 4 : 1) ; /* avoid empty segment */

PROVIDE(__end_bss_RAM3 = .) ;

} > SRAM_OC

/* BSS section for BOARD_SDRAM */

.bss_RAM4 : ALIGN(4)

{

PROVIDE(__start_bss_RAM4 = .) ;

*(.bss.$RAM4*)

*(.bss.$BOARD_SDRAM*)

. = ALIGN(4); /* avoid empty segment */

PROVIDE(__end_bss_RAM4 = .) ;

} > BOARD_SDRAM

/* MAIN BSS SECTION */

.bss : ALIGN(4)

{

_bss = .;

*(.bss*)

*(COMMON)

. = ALIGN(4) ;

_ebss = .;

PROVIDE(end = .);

} > SRAM_DTC

/* NOINIT section for SRAM_ITC */

.noinit_RAM2 (NOLOAD) : ALIGN(4)

{

*(.noinit.$RAM2*)

*(.noinit.$SRAM_ITC*)

. = ALIGN(4) ;

} > SRAM_ITC

/* NOINIT section for SRAM_OC */

.noinit_RAM3 (NOLOAD) : ALIGN(4)

{

*(.noinit.$RAM3*)

*(.noinit.$SRAM_OC*)

. = ALIGN(4) ;

} > SRAM_OC

/* NOINIT section for BOARD_SDRAM */

.noinit_RAM4 (NOLOAD) : ALIGN(4)

{

*(.noinit.$RAM4*)

*(.noinit.$BOARD_SDRAM*)

*(NonCacheable.init)

*(NonCacheable)

. = ALIGN(4) ;

} > BOARD_SDRAM

/* DEFAULT NOINIT SECTION */

.noinit (NOLOAD): ALIGN(4)

{

_noinit = .;

*(.noinit*)

. = ALIGN(4) ;

_end_noinit = .;

} > SRAM_DTC

/* Reserve and place Heap within memory map */

_HeapSize = 0x1000;

.heap : ALIGN(4)

{

_pvHeapStart = .;

. += _HeapSize;

. = ALIGN(4);

_pvHeapLimit = .;

} > SRAM_DTC

_StackSize = 0x1000;

/* Reserve space in memory for Stack */

.heap2stackfill :

{

. += _StackSize;

} > SRAM_DTC

/* Locate actual Stack in memory map */

.stack ORIGIN(SRAM_DTC) + LENGTH(SRAM_DTC) - _StackSize - 0: ALIGN(4)

{

_vStackBase = .;

. = ALIGN(4);

_vStackTop = . + _StackSize;

} > SRAM_DTC

/* Provide basic symbols giving location and size of main text

* block, including initial values of RW data sections. Note that

* these will need extending to give a complete picture with

* complex images (e.g multiple Flash banks).

*/

_image_start = LOADADDR(.text);

_image_end = LOADADDR(.data) + SIZEOF(.data);

_image_size = _image_end - _image_start;

}

|

|

发表于 2018-6-11 18:05:43

发表于 2018-6-11 18:05:43

楼主

楼主