|

Solution example 3: Use Cache maintenance functions Transmitting data: - #define TX_LENGTH (16)

- uint8_t tx_buffer[TX_LENGTH];

- /* Write data */

- tx_buffer[0] = 0x0;

- tx_buffer[1] = 0x1;

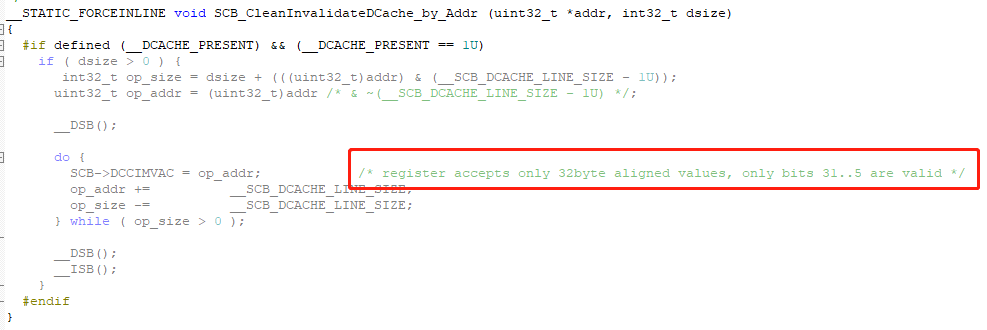

- /* Clean D-cache */

- /* Make sure the address is 32-byte aligned and add 32-bytes to length, in case it overlaps cacheline */

- SCB_CleanDCache_by_Addr((uint32_t*)(((uint32_t)tx_buffer) & ~(uint32_t)0x1F), TX_LENGTH+32);

- /* Start DMA transfer */

- HAL_UART_Transmit_DMA(&huart1, tx_buffer, TX_LENGTH);

Receiving data: - #define RX_LENGTH (16)

- uint8_t rx_buffer[RX_LENGTH];

- /* Invalidate D-cache before reception */

- /* Make sure the address is 32-byte aligned and add 32-bytes to length, in case it overlaps cacheline */

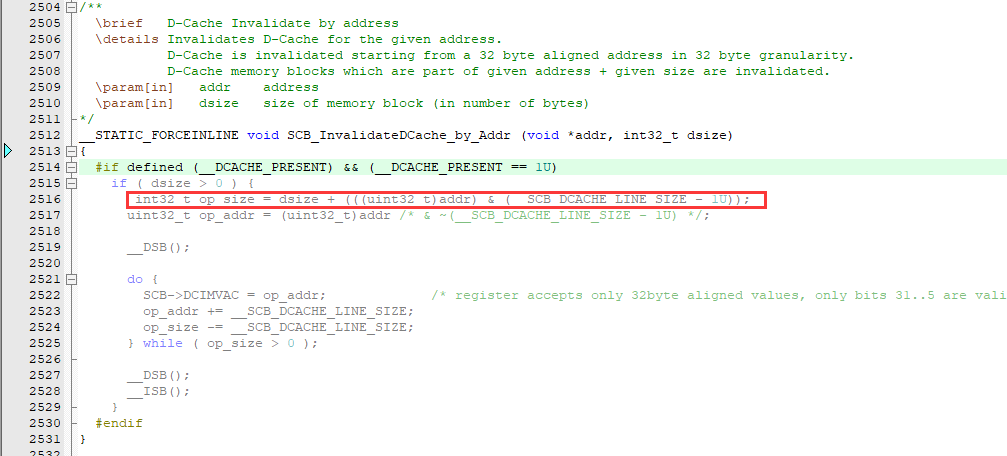

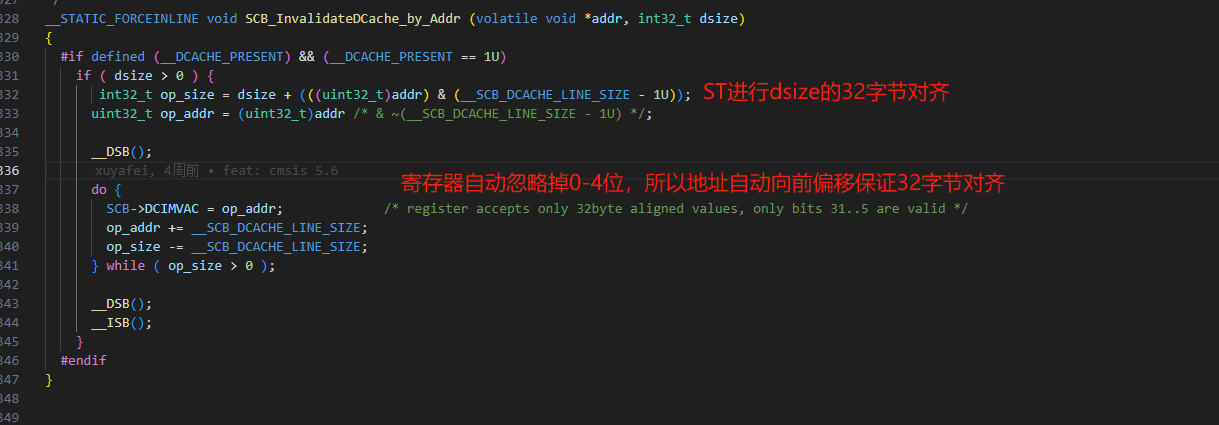

- SCB_InvalidateDCache_by_Addr((uint32_t*)(((uint32_t)rx_buffer) & ~(uint32_t)0x1F), RX_LENGTH+32);

- /* Start DMA transfer */

- HAL_UART_Receive_DMA(&huart1, rx_buffer, RX_LENGTH);

- /* No access to rx_buffer should be made before DMA transfer is completed */

Please note that in case of reception there can be problem if rx_buffer is not aligned to the size of cache-line (32-bytes), because during the invalidate operation another data sharing the same cache-line(s) with rx_buffer can be lost.

参考文献: https://community.st.com/s/article/FAQ-DMA-is-not-working-on-STM32H7-devices

|

发表于 2018-11-3 02:08:00

发表于 2018-11-3 02:08:00

发表于 2018-11-3 09:45:00

发表于 2018-11-3 09:45:00

,偶尔就会出点问题

,偶尔就会出点问题 楼主

楼主

,感谢向前偏移会导致数据刷新错误

,感谢向前偏移会导致数据刷新错误