|

|

发表于 2024-2-6 21:55:34

|

显示全部楼层

发表于 2024-2-6 21:55:34

|

显示全部楼层

对四种策略(write through, write back, read allocate, write allocate)的个人理解:

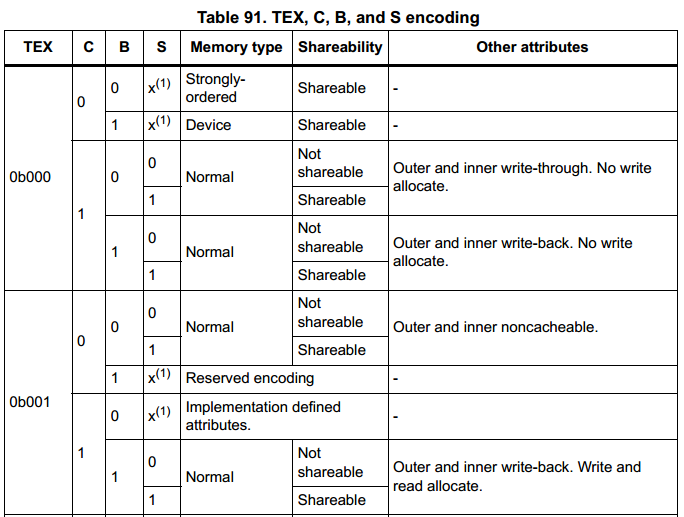

- C=0时等同于Non-cacheable。

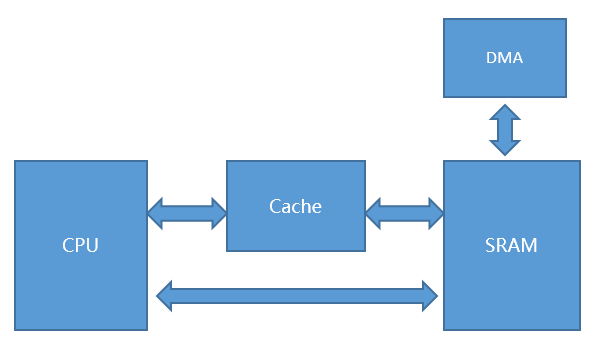

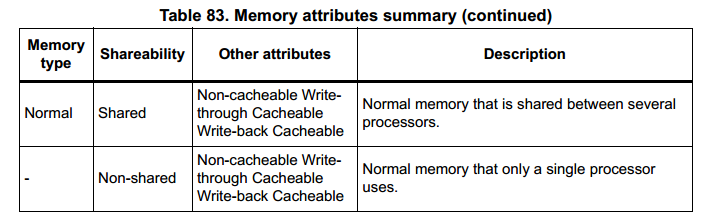

- 启用缓存时(C=1), write through/write back是由B(Bufferable)位决定的,B=0时用write through, B=1用write back,两个策略的区别在于前者CPU写的SRAM数据如果在Cache有开辟对应的区域(cache hit),那么写进Cache的时候同时也会写到SRAM,后者不会,因此后者在读cache的时候如果dma有更新SRAM,数据就会不一致。

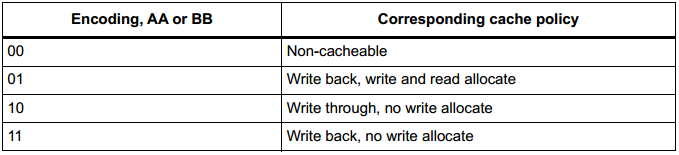

- read/write allocate的用处是在CPU cache miss,与SRAM交互数据(写入SRAM或者从SRAM读)时,决定数据是否也同步到Cache的,如果No allocate就不会同步回Cache,C=1下的四种策略均有read allocate, 而write allocate对应TEX,TEX=000为no write allocate, TEX=001为write allocate.

- 看表格,write through(B=0)和write allocate(TEX=001)似乎是不兼容的,一个是CPU在cache hit时写cache同时更新SRAM,另一个是在CPU cache miss时写SRAM同时更新到cache, 个人理解如果两个属性都有,cache初始是空的,系统第一次写肯定cache miss,这时候是写SRAM再同步到cache,后面写就都是cache hit了,如果write through的话就会写cache同时也会写到SRAM,这样write allocate反而就没什么用了。

|

|

发表于 2018-11-6 00:23:46

发表于 2018-11-6 00:23:46

发表于 2018-11-6 07:53:25

发表于 2018-11-6 07:53:25

楼主

楼主