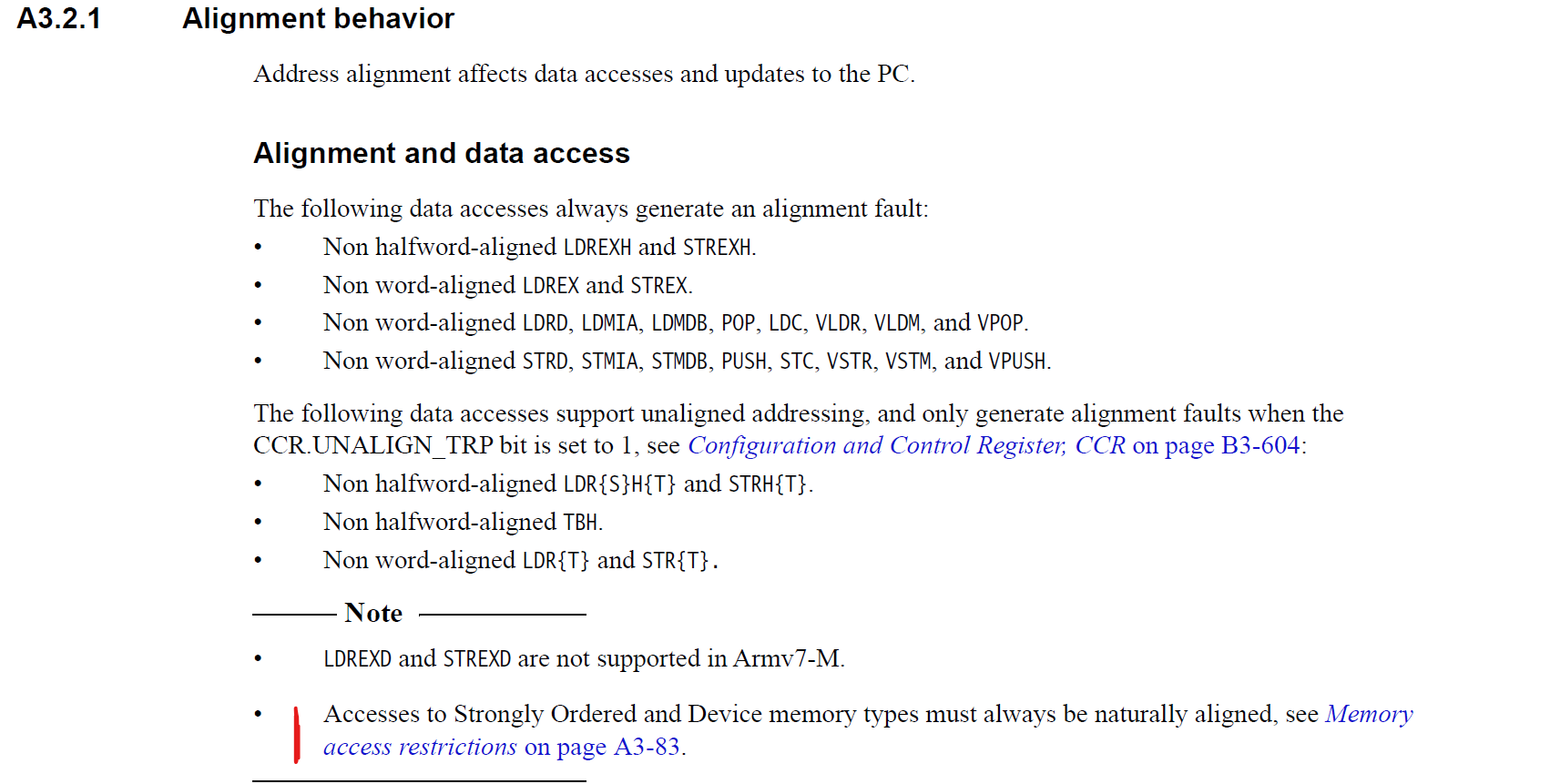

测试了下F407, 配置为Strongly Order或者Device都没问题,没有这个问题。

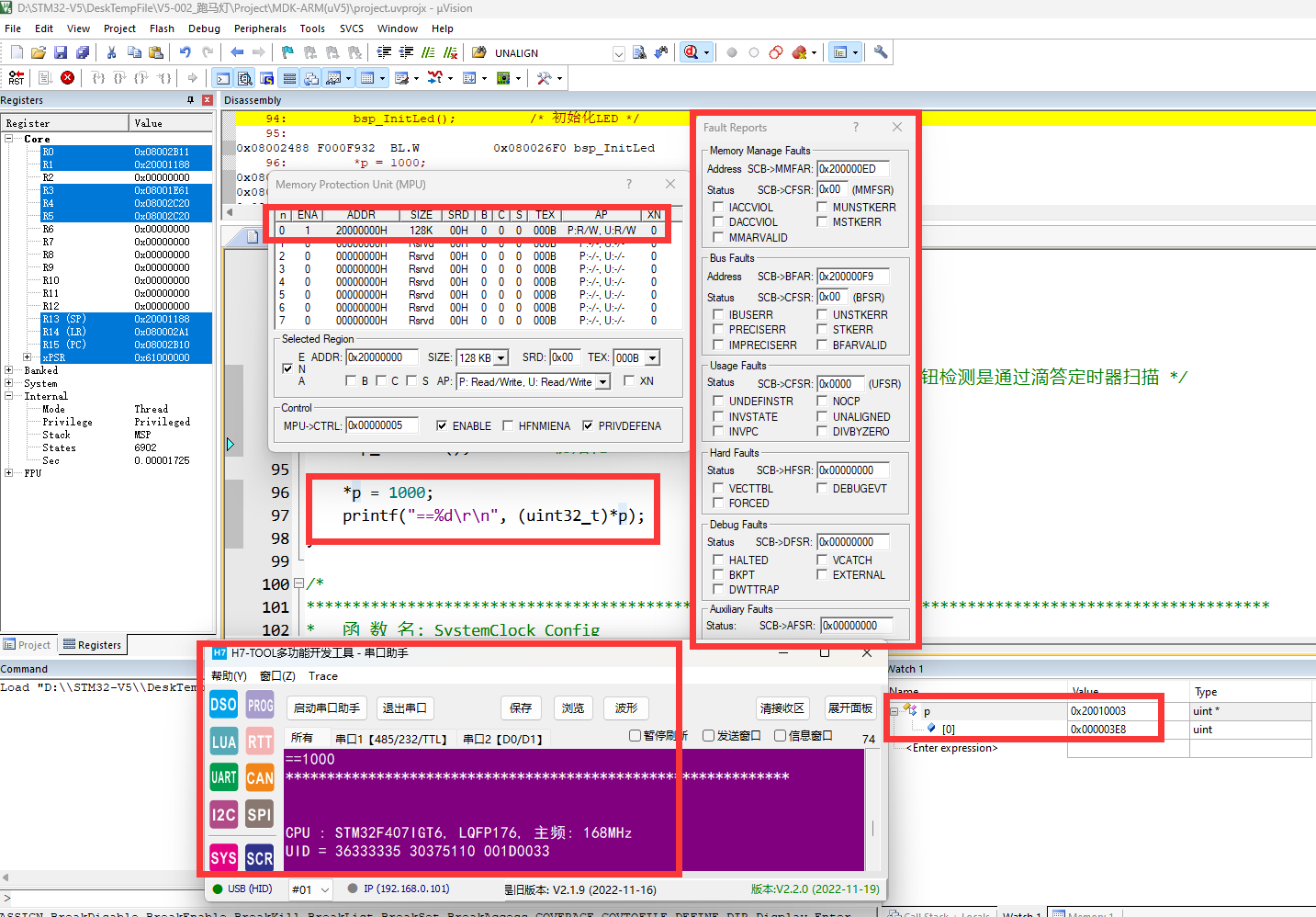

配置MPU

[C] 纯文本查看 复制代码 MPU_Region_InitTypeDef MPU_InitStruct;

/* 禁止 MPU */

HAL_MPU_Disable();

MPU_InitStruct.Enable = MPU_REGION_ENABLE;

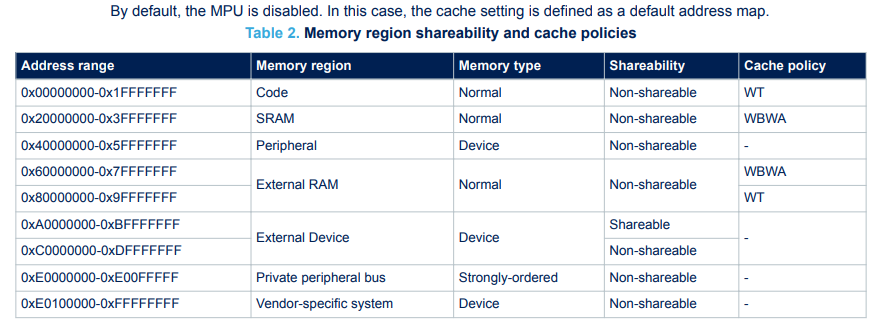

MPU_InitStruct.BaseAddress = 0x20000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_128KB;

MPU_InitStruct.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_InitStruct.IsBufferable = MPU_ACCESS_NOT_BUFFERABLE;

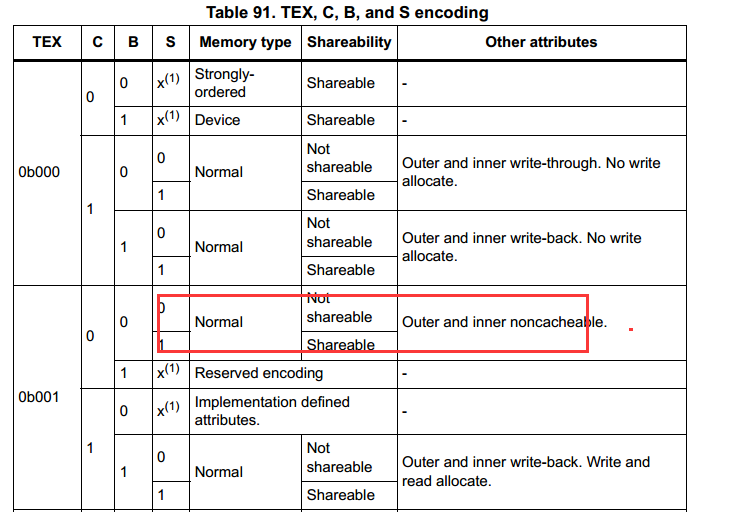

MPU_InitStruct.IsCacheable = MPU_ACCESS_NOT_CACHEABLE;

MPU_InitStruct.IsShareable = MPU_ACCESS_NOT_SHAREABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER0;

MPU_InitStruct.TypeExtField = MPU_TEX_LEVEL0;

MPU_InitStruct.SubRegionDisable = 0x00;

MPU_InitStruct.DisableExec = MPU_INSTRUCTION_ACCESS_ENABLE;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

/*使能 MPU */

HAL_MPU_Enable(MPU_PRIVILEGED_DEFAULT);

测试:

[C] 纯文本查看 复制代码 *p = 1000;

printf("==%d\r\n", (uint32_t)*p);

|

发表于 2019-7-23 01:03:44

发表于 2019-7-23 01:03:44

楼主

楼主 发表于 2019-7-23 11:37:39

发表于 2019-7-23 11:37:39

发表于 2019-7-23 15:40:41

发表于 2019-7-23 15:40:41

,我们应该改个标题

,我们应该改个标题