|

|

发表于 2022-2-14 11:19:34

|

显示全部楼层

发表于 2022-2-14 11:19:34

|

显示全部楼层

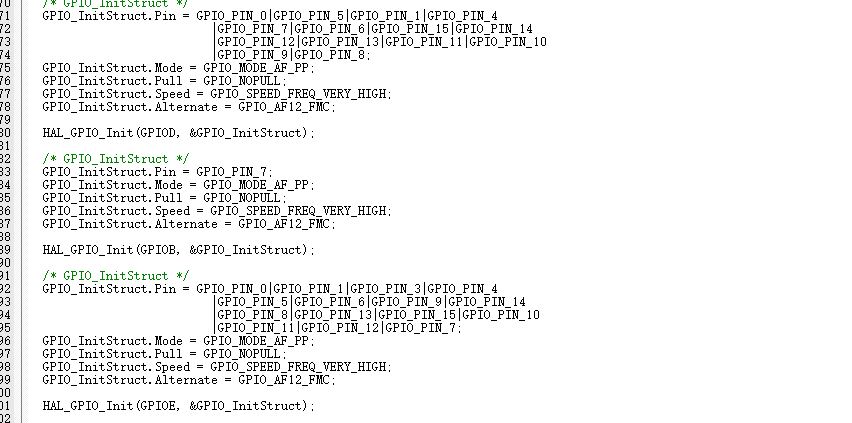

代码部分:

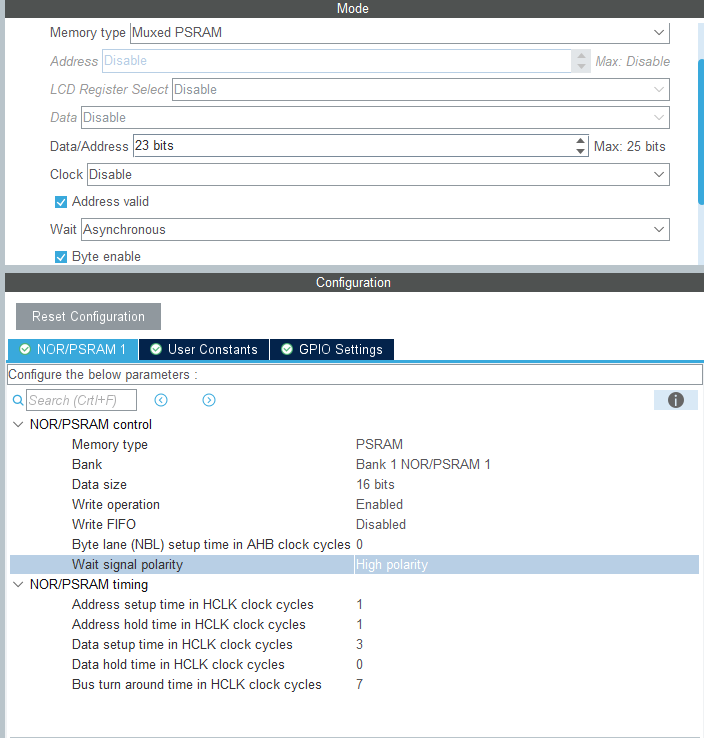

hsram1.Instance = FMC_NORSRAM_DEVICE;

hsram1.Extended = FMC_NORSRAM_EXTENDED_DEVICE;

/* hsram1.Init */

hsram1.Init.NSBank = FMC_NORSRAM_BANK1;

hsram1.Init.DataAddressMux = FMC_DATA_ADDRESS_MUX_ENABLE;

hsram1.Init.MemoryType = FMC_MEMORY_TYPE_PSRAM;

hsram1.Init.MemoryDataWidth = FMC_NORSRAM_MEM_BUS_WIDTH_16;

hsram1.Init.BurstAccessMode = FMC_BURST_ACCESS_MODE_DISABLE;

hsram1.Init.WaitSignalPolarity = FMC_WAIT_SIGNAL_POLARITY_HIGH;

hsram1.Init.WaitSignalActive = FMC_WAIT_TIMING_BEFORE_WS;

hsram1.Init.WriteOperation = FMC_WRITE_OPERATION_ENABLE;

hsram1.Init.WaitSignal = FMC_WAIT_SIGNAL_DISABLE;

hsram1.Init.ExtendedMode = FMC_EXTENDED_MODE_DISABLE;

hsram1.Init.AsynchronousWait = FMC_ASYNCHRONOUS_WAIT_ENABLE;

hsram1.Init.WriteBurst = FMC_WRITE_BURST_DISABLE;

hsram1.Init.ContinuousClock = FMC_CONTINUOUS_CLOCK_SYNC_ONLY;

hsram1.Init.WriteFifo = FMC_WRITE_FIFO_DISABLE;

hsram1.Init.NBLSetupTime = 0;

hsram1.Init.PageSize = FMC_PAGE_SIZE_NONE;

/* Timing */

Timing.AddressSetupTime = 1;

Timing.AddressHoldTime = 1;

Timing.DataSetupTime = 3;

Timing.DataHoldTime = 0;

Timing.BusTurnAroundDuration = 7;

Timing.CLKDivision = 16;

Timing.DataLatency = 17;

Timing.AccessMode = FMC_ACCESS_MODE_A;

/* ExtTiming */

if (HAL_SRAM_Init(&hsram1, &Timing, NULL) != HAL_OK)

{

Error_Handler( );

}

/* USER CODE BEGIN FMC_Init 2 */

LOG_I("HAL_SRAM_Init");

uint16_t ASP_RCR = 0,ASP_DIDR = 0,ASP_BCR = 0;

// HAL_SRAM_Read_16b(&hsram1, (uint32_t*)SRAM_ADDR, &ASP_RCR, 1);

// HAL_SRAM_Read_16b(&hsram1, (uint32_t*)(SRAM_ADDR | APS_BCR_ADDR), &ASP_BCR, 1);

// HAL_SRAM_Read_16b(&hsram1, (uint32_t*)(SRAM_ADDR | APS_DIDR_ADDR), &ASP_DIDR, 1);

ASP_RCR = *(__IO uint16_t*)(SRAM_ADDR);

ASP_DIDR = *(__IO uint16_t*)(SRAM_ADDR | APS_DIDR_ADDR);

ASP_BCR = *(__IO uint16_t *)(SRAM_ADDR | APS_BCR_ADDR);

LOG_I("ASP_RCR: %4X", ASP_RCR);

LOG_I("ASP_DIDR: %4X", ASP_DIDR);

LOG_I("ASP_BCR: %4X", ASP_BCR);

*(__IO uint16_t*)(SRAM_ADDR | APS_DIDR_ADDR) = 0x9D1F;

|

|

发表于 2019-12-27 11:24:37

发表于 2019-12-27 11:24:37

发表于 2019-12-27 11:52:39

发表于 2019-12-27 11:52:39

楼主

楼主

发表于 2022-2-16 11:33:16

发表于 2022-2-16 11:33:16