|

|

楼主 |

发表于 2020-1-14 12:25:47

|

显示全部楼层

你好,是 fs_config.h 里面的

#if (NAND0_ENABLE)

static NAND_MEDIA_HANDLE fs_nand0_media_handle;

#ifndef RTE_FileSystem_Debug

static

#endif

NAND_FTL_DEV fs_nand0_handle;

#if (NAND0_SW_ECC == 2)

#define NAND0_ECC_ONCHIP 1

#else

#define NAND0_ECC_ONCHIP 0

#endif

#endif

#if (NAND1_ENABLE)

static NAND_MEDIA_HANDLE fs_nand1_media_handle;

#ifndef RTE_FileSystem_Debug

static

#endif

NAND_FTL_DEV fs_nand1_handle;

#if (NAND1_SW_ECC == 2)

#define NAND1_ECC_ONCHIP 1

#else

#define NAND1_ECC_ONCHIP 0

#endif

#endif

#if (NAND0_ENABLE || NAND1_ENABLE)

extern void nand_DrvEvent (uint32_t event, NAND_MEDIA_HANDLE *h);

extern void nand_MediaEvent (NAND_FTL_DEV *ftl);

#endif

#ifdef RTE_FileSystem_Drive_NAND_0

#if (NAND0_ENABLE)

extern ARM_DRIVER_NAND CREATE_SYMBOL (Driver_NAND, NAND0_DRIVER);

static NAND_HW_DRIVER fs_nand0_hw_driver;

#if ((NAND1_ENABLE) && (NAND1_DRIVER == NAND0_DRIVER))

#if (NAND1_DEV_NUM == NAND0_DEV_NUM)

#error "::File System rive:NAND: NAND ports for different drives must be different" rive:NAND: NAND ports for different drives must be different"

#endif

#define NAND0_DEVICE1

/* NAND0 Device1 Configuration Part */

#define NAND1_MEDIA_EVENT_HANDLER NAND0_Media_SignalEventHandler

#define NAND1_HW_EVENT_HANDLER NAND0_HW_SignalEventHandler

#define NAND1_HW_DRIVER fs_nand0_hw_driver

#define NAND1_DRIVER_CONFIG 0

#endif

static void NAND0_HW_SignalEventHandler (uint32_t dev_num, uint32_t event) {

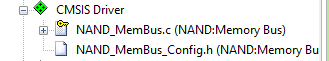

/* Event from "CMSIS Driver" to "NAND Media Layer" */

switch (dev_num) {

case NAND0_DEV_NUM: nand_DrvEvent (event, &fs_nand0_media_handle); break;

#if defined(NAND0_DEVICE1)

case NAND1_DEV_NUM: nand_DrvEvent (event, &fs_nand1_media_handle); break;

#endif

default: return;

}

}

static void NAND0_Media_SignalEventHandler (uint32_t dev_num, uint32_t event) {

(void)event;

/* Event from "NAND Media Layer" to "NAND Flash Translation Layer" */

switch (dev_num) {

case NAND0_DEV_NUM: nand_MediaEvent (&fs_nand0_handle); break;

#if defined(NAND0_DEVICE1)

case NAND1_DEV_NUM: nand_MediaEvent (&fs_nand1_handle); break;

#endif

default: return;

}

}

#endif

#endif

#ifdef RTE_FileSystem_Drive_NAND_1

#if (((NAND0_ENABLE == 0) && NAND1_ENABLE) || ((NAND0_ENABLE && NAND1_ENABLE) && (NAND1_DRIVER != NAND0_DRIVER)))

extern ARM_DRIVER_NAND CREATE_SYMBOL (Driver_NAND, NAND1_DRIVER);

static NAND_HW_DRIVER fs_nand1_hw_driver;

/* NAND1 Device0 Configuration Part */

#define NAND1_MEDIA_EVENT_HANDLER NAND1_Media_SignalEventHandler

#define NAND1_HW_EVENT_HANDLER NAND1_HW_SignalEventHandler

#define NAND1_HW_DRIVER fs_nand1_hw_driver

#define NAND1_DRIVER_CONFIG 1

static void NAND1_HW_SignalEventHandler (uint32_t dev_num, uint32_t event) {

/* Event from "CMSIS Driver" to "NAND Media Layer" */

switch (dev_num) {

case NAND1_DEV_NUM: nand_DrvEvent (event, &fs_nand1_media_handle); break;

default: return;

}

}

static void NAND1_Media_SignalEventHandler (uint32_t dev_num, uint32_t event) {

(void)event;

/* Event from "NAND Media Layer" to "NAND Flash Translation Layer" */

switch (dev_num) {

case NAND1_DEV_NUM: nand_MediaEvent (&fs_nand1_handle); break;

default: return;

}

}

#endif

#endif

/*----------------------------------------------------------------------------

* Drive N0: NAND Flash device NAND0 configuration

*---------------------------------------------------------------------------*/

#if (NAND0_ENABLE)

extern ARM_DRIVER_NAND CREATE_SYMBOL (Driver_NAND, NAND0_DRIVER);

#if (NAND0_CACHE_RELOC == 1)

#define __AT_NAND0 __MEMORY_AT(NAND0_CACHE_ADDR)

#else

#define __AT_NAND0

#endif

/* NAND Cache Buffer for FAT, Page and Block Caching */

#define NAND0_CSZ ((NAND0_CACHE_SIZE + 1) * 1024 + \

(NAND0_PAGE_CACHE + 2) * NAND0_PAGE_SIZE + \

(NAND0_BLOCK_CACHE + 2) * NAND0_PAGE_COUNT)

#define NAND0_FSJBUF (NAND0_FAT_JOURNAL * 512)

static uint32_t nand0_cache[NAND0_CSZ/4 + NAND0_FSJBUF/4] __AT_NAND0;

static PAGE_CACHE nand0_capg [NAND0_PAGE_CACHE + 1];

static BLOCK_CACHE nand0_cabl [NAND0_BLOCK_CACHE + 2];

static uint32_t nand0_ttsn [NAND_TSN_SIZE(NAND0_BLOCK_COUNT, NAND0_PAGE_SIZE)];

#if !defined (fs_nand0_mtx)

#error "Mutex object for drive N0 is undefined."

#endif

static fsFAT_Volume fs_nand0_vol;

#if (NAND0_FAT_JOURNAL)

static FSJOUR fs_nand0_fsj;

#endif

#if (NAND0_NAME_CACHE_SIZE > 0)

#define NAND0_NAME_CACHE_MAX_DEPTH 8

#define NAND0_NAME_CACHE_BUF_SIZE ((NAND0_NAME_CACHE_SIZE * FAT_NCACHE_LINK_SZ) + \

(NAND0_NAME_CACHE_MAX_DEPTH * FAT_NCACHE_USED_SZ) + \

FAT_NCACHE_STAT_SZ)

static uint32_t nand0_ncache_buf[NAND0_NAME_CACHE_BUF_SIZE/4];

static NCACHE nand0_ncache = {

NAND0_NAME_CACHE_MAX_DEPTH,

NAND0_NAME_CACHE_BUF_SIZE,

nand0_ncache_buf

};

#endif

#if (NAND0_ECC_ONCHIP != 0)

#define NAND0_ECC_TYPE 2 /* On-chip ECC uses ECC0 over Main+Spare */

#define NAND0_ECC_PAGE_SIZE 15 /* Use virtual_page_size definitions */

#define NAND0_ECC_RESERVED 0 /* Reserved bits must be zero */

#define NAND0_ECC_CORRECT_BITS 0 /* Correctability level is not relevant */

#define NAND0_ECC_MAIN_CW_OFFS 0 /* Main area starts at page start */

#if (NAND0_ECC_VPAGE_LAYOUT == 0) /* Layout defines gap between each main */

#define NAND0_ECC_MAIN_CW_GAP NAND0_ECC_VSPARE_SIZE

#else

#define NAND0_ECC_MAIN_CW_GAP 0

#endif

static const ARM_NAND_ECC_INFO nand0_ecc = {

(NAND0_ECC_TYPE & 0x0003),

(NAND0_ECC_VPAGE_LAYOUT & 0x0001),

(NAND0_ECC_VPAGE_COUNT & 0x0007),

(NAND0_ECC_PAGE_SIZE & 0x000F),

(NAND0_ECC_RESERVED & 0x3FFF),

(NAND0_ECC_CORRECT_BITS & 0x00FF),

{ NAND0_ECC_MAIN_CW_SIZE, NAND0_ECC_SPARE_CW_SIZE },

{ NAND0_ECC_DATA_SIZE, 0 },

{ NAND0_ECC_DATA_OFFS, 0 },

{ NAND0_ECC_VMAIN_SIZE, NAND0_ECC_VSPARE_SIZE },

{ NAND0_ECC_MAIN_CW_OFFS, NAND0_ECC_SPARE_CW_OFFS },

{ NAND0_ECC_MAIN_CW_GAP, NAND0_ECC_SPARE_CW_GAP },

{ NAND0_ECC_DATA_GAP, 0 }

};

#endif

static const NAND_DEVICE nand0_device = {

&fs_nand0_handle.PgLay,

NAND0_BUS_WIDTH,

NAND0_DEV_NUM,

NAND0_PAGE_SIZE,

NAND0_BLOCK_COUNT,

NAND0_PAGE_COUNT,

NAND_SEC_BLOCK (NAND0_PAGE_COUNT, NAND0_PAGE_SIZE),

NAND_SEC_PAGE (NAND0_PAGE_SIZE),

NAND_ROW_CYCLES (NAND0_BLOCK_COUNT, NAND0_PAGE_COUNT),

NAND_COL_CYCLES (NAND0_PAGE_SIZE),

NAND0_SW_ECC,

#if (NAND0_ECC_ONCHIP != 0)

&nand0_ecc

#else

NULL

#endif

};

/* NAND Flash Configuration */

static NAND_FTL_CFG nand0_cfg = {

/* Block Translation Table Space */

1,

NAND_BTT_SIZE (NAND0_BLOCK_COUNT),

/* Data Space */

NAND_BTT_SIZE (NAND0_BLOCK_COUNT) + 1,

NAND0_BLOCK_COUNT - 1,

/* Caching */

NAND0_BLOCK_CACHE + 2,

NAND0_PAGE_CACHE + 1,

NAND_TSN_SIZE(NAND0_BLOCK_COUNT, NAND0_PAGE_SIZE),

{ 0, 0 },

/* Page buffer & Caches */

(uint8_t *)&nand0_cache[(NAND0_CACHE_SIZE+1)*256],

&nand0_cabl[0],

(uint8_t *)&nand0_cache[(NAND0_CACHE_SIZE+1)*256+(NAND0_PAGE_CACHE+2)*NAND0_PAGE_SIZE/4],

&nand0_capg[0],

(uint8_t *)&nand0_cache[(NAND0_CACHE_SIZE+1)*256+NAND0_PAGE_SIZE/4],

&nand0_ttsn[0]

};

/* NAND0 wrapper functions */

static uint32_t nand0_Init (uint32_t mode) {

return (ftl_Init (mode, &fs_nand0_handle));

}

static uint32_t nand0_UnInit (uint32_t mode) {

return (ftl_UnInit (mode, &fs_nand0_handle));

}

static uint32_t nand0_RdSect (uint32_t sect, uint8_t *buf, uint32_t cnt) {

uint32_t retv = ftl_ReadSect (sect, buf, cnt, &fs_nand0_handle);

if (retv < 2) return (true);

else return (false);

}

static uint32_t nand0_WrSect (uint32_t sect, const uint8_t *buf, uint32_t cnt) {

uint32_t retv = ftl_WriteSect (sect, buf, cnt, &fs_nand0_handle);

if (retv < 2) return (true);

else return (false);

}

static uint32_t nand0_RdInfo (fsMediaInfo *info) {

return (ftl_ReadInfo (info, &fs_nand0_handle));

}

static fsStatus nand0_DevCtrl (fsDevCtrlCode code, void *p) {

return (ftl_DevCtrl (code, p, &fs_nand0_handle));

}

static FAT_DRV fs_nand0_drv = {

nand0_Init,

nand0_UnInit,

nand0_RdSect,

nand0_WrSect,

nand0_RdInfo,

nand0_DevCtrl

};

#endif

是这几个函数吧,貌似感觉移植起来比较麻烦啊

|

|

发表于 2020-1-14 09:24:00

发表于 2020-1-14 09:24:00

发表于 2020-1-14 09:42:14

发表于 2020-1-14 09:42:14

楼主

楼主

rive:NAND: NAND ports for different drives must be different"

rive:NAND: NAND ports for different drives must be different"